赛灵思 SDSoC 开发环境介绍

时间:03-11

来源:互联网

点击:

前言

随着智能系统的进步和“ 物联网”的发展,以及人与物之间互联互通的增强,大多数新产品现在均采用了基于SoC 的开发平台。此类平台便于企业以更快的速度将产品推向市场,提高系统级效率,而且最重要的是便于实现持续的创新和产品差异化。

为实现投资回报最大化,设计团队必须精心选择实现产品差异化的方法,同时还必须满足日益增长的市场需求和严苛的成本目标要求。真正的平台差异化依赖于新的软件特性与新的硬件特性的组合。鉴于加速产品上市这一要求实际上在各层面均存在差异化,因此需要工具和环境能够在不影响架构和性能的条件下,用传统ASSP 编程环境所拥有的完整性和易用性实现软硬件的差异化。

就当前的硬件差异化而言,许多平台开发人员使用FPGA 实现任意(Any-to-Any)互连。其中的可编程逻辑用于将平台的处理器连接到PCIe® 和以太网等标准接口上。此外,许多系统也将FPGA 作为用于实现关键功能和算法加速的协处理器。与在标准处理器上运行相比,可编程逻辑的并行架构可提供高达100 倍以上的性能优势。

2011 年推出的Zynq®-7000 全可编程SoC 和目前新推出的Zynq UltraScale+™MPSoC,分别采用先进的28nm 工艺节点和16nm 工艺节点,将强大的ARM® 处理系统和可编程逻辑完美结合在了一起。随着这两款产品的问世,赛灵思现可提供完全取代传统处理器和特定领域专用SoC 的业经验证的替代产品。Zynq SoC和MPSoC 能够在降低材料清单成本的同时提升系统性能并降低系统功耗。

赛灵思SDSoC 开发环境介绍

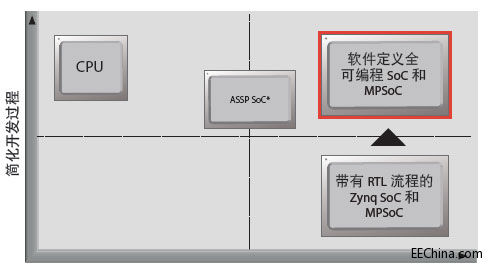

Zynq SoC 和MPSoC 与软件工程师和FPGA 硬件工程师共同组成的设计团队可谓天合之作。但其对于硬件资源有限或欠缺的团队来说,使用起来很有难度,因为需要具备RTL(VHDL或Verilog)开发专业知识才能充分发挥该器件的优势。为解决这一难题,让更多的设计团队能够利用Zynq 器件的优势,赛灵思推出了一种全新的C/C++ 开发环境SDSoC™。SDSoC开发环境是赛灵思SDxTM 系列开发环境的第三大成员,能够让更广泛的嵌入式软件开发人员发挥软硬件“ 全可编程”器件的威力。

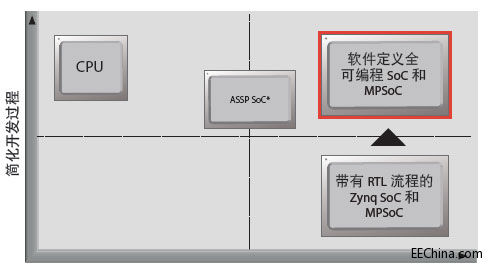

SDSoC 带来的软件定义机遇

C/C++ 环境提供类似ASSP 的编程体验

性能功耗比和任意互连

* 重点领域(例如图像/ 视频、SDR 等)

注:软件可编程器件往往与FPGA 结合使用,以实现连接和协处理功能

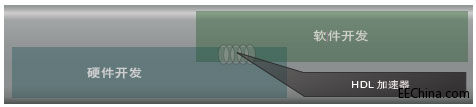

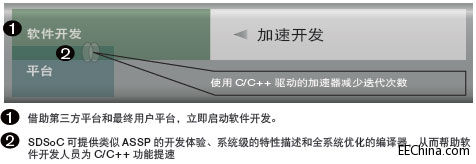

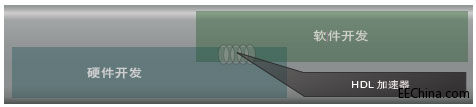

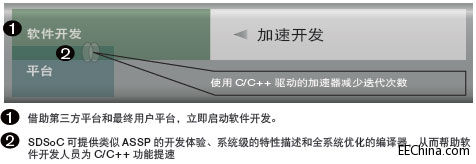

SDSoC 开发环境可通过两种方式加速Zynq SoC 和MPSoC 开发进程。第一种是,软件开发人员借助赛灵思平台、第三方平台

或最终用户平台,可以比使用传统硬件/ 传统软件开发流程更快地启动开发。第二种是,SDSoC 可以消除在将可编程逻辑用作

软件加速器时软件团队和硬件团队之间常发生的反复变更,真正加速整体系统开发进程。

传统开发进度

软件定义开发进程

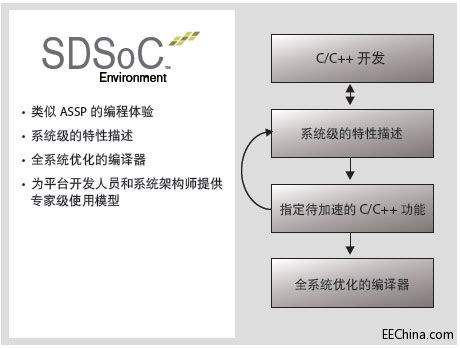

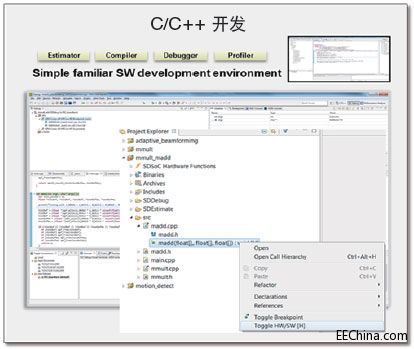

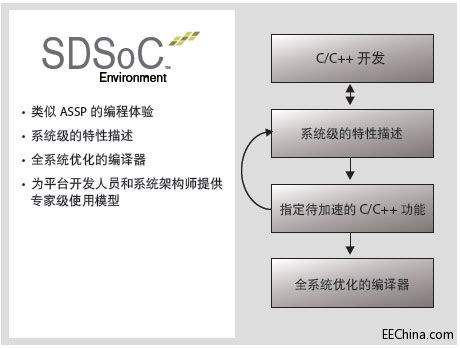

SDSoC 开发环境可提供高度简化、类似ASSP C/C++ 的编程体验,包括简便易用的Eclipse 集成设计环境(IDE)和用于异构Zynq 平台部署的综合开发平台。SDSoC 配有业界首款C/C++ 全系统优化的编译器,可提供系统级的特性描述、可编程逻辑内自动软件加速、自动系统连接生成,以及用于加快编程速度的各种库。此外,SDSoC 还可为客户和第三方平台开发人员提供专门的流程,以便在SDSoC 开发环境中使用这些平台。

SDSoC 开发环境

类似ASSP 的编程体验

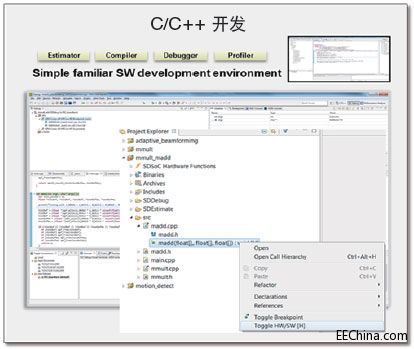

SDSoC 可供系统和嵌入式软件开发人员使用,其提供的Eclipse IDE 可用于开发运行于裸机或Linux 和FreeRTOS 等操作系统上的C/C++ 应用。SDSoC 可用于开发各种完整的异构多处理系统,包括运行在ARM/NEON 处理器上的软件和可编程逻辑中的软件加速器,还能将现有的HDL IP 模块反复用作C 语言可调用的库。与传统的单独以硬件为中心的流程和以软件为中心的流程不同,这两种流程可能会导致开发延迟、系统架构与性能的不确定性,而SDSoC 在开发人员熟悉的嵌入式框架中实现快速系统特性描述和可编程逻辑软件加速。

这款简便易用的IDE 可提供项目创建向导,供用户选择目标平台和操作系统,并使用模板创建功能齐全的SDSoC 项目,作为构建自己应用的起点。

此外,SDSoC 还可为软件团队提供简单的GUI 选项,用于选择在可编程逻辑中加速的功能。SDSoC 编译器将生成准备在目标平台板上运行的所有必备硬件和软件。

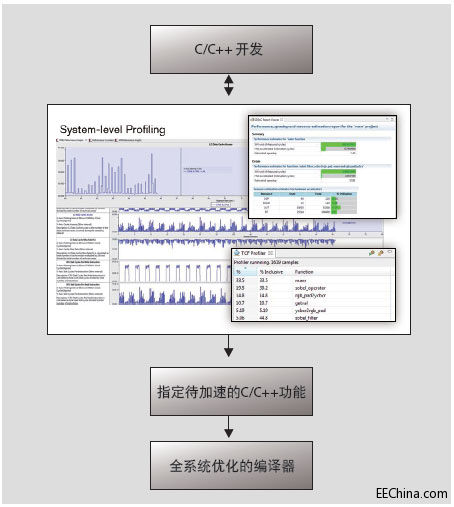

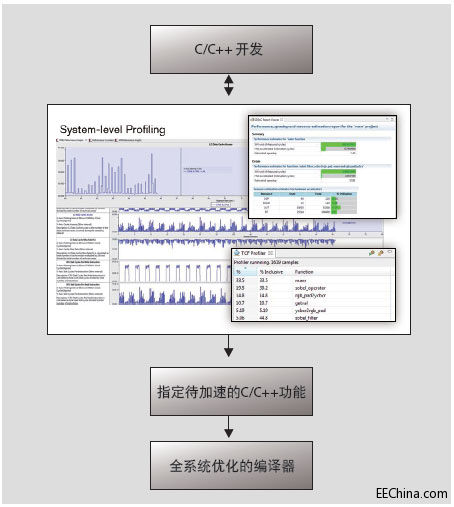

系统级的特性描述

以赛灵思软件开发套件(SDK)目前提供的高级软件特性描述为基础,SDSoC 增添了系统级特性描述,用于快速系统(软/ 硬件)性能估算。此外,还能快速生成并探索系统级架构,以实现最佳总体系统性能与功耗。

SDSoC 采用基于PC 采样的非侵入式编译器和标准的GPROF 编译器,能帮助用户配置其自身软件应用,以识别占用时间最多且适用于硬件加速的功能。

此外,SDSoC 还增添了快速系统(软/ 硬件)性能和器件利用率估算功能,能够迅速完成系统级架构探索,以实现最佳性能、资源利用率和功耗。用户可在可编程逻辑中设定待加速的功能,而且SDSoC 还能调用C/C++ 代码来报告软件周期、硬件周期、数据传输估算、总体应用加速以及硬件资源利用率等情况。

充分利用基于平台的性能估算流程,软件开发人员能够在数分钟内迅速估算出将一项或多项软件功能转移到硬件中用于加速所产生的性能影响,而实际的硬件生成则需要一小时甚至更长时间。

在目标平台上,SDSoC 使用由ARM CPU 提供的性能计数器,同时自动插入AXI 性能监控器(APM)到可编程逻辑中以采集硬件性能数据,可为缓存、存储器、软件加速器和总线利用率提供自动性能测量。运行在平台上的软件可采集性能数据,SDSoC 就使用该数据帮助识别系统中的性能瓶颈。这种快速的性能反馈能实现最佳代码分区,以满足系统级性能和功耗需求,同时将开发流程缩短数周时间。

随着智能系统的进步和“ 物联网”的发展,以及人与物之间互联互通的增强,大多数新产品现在均采用了基于SoC 的开发平台。此类平台便于企业以更快的速度将产品推向市场,提高系统级效率,而且最重要的是便于实现持续的创新和产品差异化。

为实现投资回报最大化,设计团队必须精心选择实现产品差异化的方法,同时还必须满足日益增长的市场需求和严苛的成本目标要求。真正的平台差异化依赖于新的软件特性与新的硬件特性的组合。鉴于加速产品上市这一要求实际上在各层面均存在差异化,因此需要工具和环境能够在不影响架构和性能的条件下,用传统ASSP 编程环境所拥有的完整性和易用性实现软硬件的差异化。

就当前的硬件差异化而言,许多平台开发人员使用FPGA 实现任意(Any-to-Any)互连。其中的可编程逻辑用于将平台的处理器连接到PCIe® 和以太网等标准接口上。此外,许多系统也将FPGA 作为用于实现关键功能和算法加速的协处理器。与在标准处理器上运行相比,可编程逻辑的并行架构可提供高达100 倍以上的性能优势。

2011 年推出的Zynq®-7000 全可编程SoC 和目前新推出的Zynq UltraScale+™MPSoC,分别采用先进的28nm 工艺节点和16nm 工艺节点,将强大的ARM® 处理系统和可编程逻辑完美结合在了一起。随着这两款产品的问世,赛灵思现可提供完全取代传统处理器和特定领域专用SoC 的业经验证的替代产品。Zynq SoC和MPSoC 能够在降低材料清单成本的同时提升系统性能并降低系统功耗。

赛灵思SDSoC 开发环境介绍

Zynq SoC 和MPSoC 与软件工程师和FPGA 硬件工程师共同组成的设计团队可谓天合之作。但其对于硬件资源有限或欠缺的团队来说,使用起来很有难度,因为需要具备RTL(VHDL或Verilog)开发专业知识才能充分发挥该器件的优势。为解决这一难题,让更多的设计团队能够利用Zynq 器件的优势,赛灵思推出了一种全新的C/C++ 开发环境SDSoC™。SDSoC开发环境是赛灵思SDxTM 系列开发环境的第三大成员,能够让更广泛的嵌入式软件开发人员发挥软硬件“ 全可编程”器件的威力。

SDSoC 带来的软件定义机遇

C/C++ 环境提供类似ASSP 的编程体验

性能功耗比和任意互连

* 重点领域(例如图像/ 视频、SDR 等)

注:软件可编程器件往往与FPGA 结合使用,以实现连接和协处理功能

SDSoC 开发环境可通过两种方式加速Zynq SoC 和MPSoC 开发进程。第一种是,软件开发人员借助赛灵思平台、第三方平台

或最终用户平台,可以比使用传统硬件/ 传统软件开发流程更快地启动开发。第二种是,SDSoC 可以消除在将可编程逻辑用作

软件加速器时软件团队和硬件团队之间常发生的反复变更,真正加速整体系统开发进程。

传统开发进度

软件定义开发进程

SDSoC 开发环境可提供高度简化、类似ASSP C/C++ 的编程体验,包括简便易用的Eclipse 集成设计环境(IDE)和用于异构Zynq 平台部署的综合开发平台。SDSoC 配有业界首款C/C++ 全系统优化的编译器,可提供系统级的特性描述、可编程逻辑内自动软件加速、自动系统连接生成,以及用于加快编程速度的各种库。此外,SDSoC 还可为客户和第三方平台开发人员提供专门的流程,以便在SDSoC 开发环境中使用这些平台。

SDSoC 开发环境

类似ASSP 的编程体验

SDSoC 可供系统和嵌入式软件开发人员使用,其提供的Eclipse IDE 可用于开发运行于裸机或Linux 和FreeRTOS 等操作系统上的C/C++ 应用。SDSoC 可用于开发各种完整的异构多处理系统,包括运行在ARM/NEON 处理器上的软件和可编程逻辑中的软件加速器,还能将现有的HDL IP 模块反复用作C 语言可调用的库。与传统的单独以硬件为中心的流程和以软件为中心的流程不同,这两种流程可能会导致开发延迟、系统架构与性能的不确定性,而SDSoC 在开发人员熟悉的嵌入式框架中实现快速系统特性描述和可编程逻辑软件加速。

这款简便易用的IDE 可提供项目创建向导,供用户选择目标平台和操作系统,并使用模板创建功能齐全的SDSoC 项目,作为构建自己应用的起点。

此外,SDSoC 还可为软件团队提供简单的GUI 选项,用于选择在可编程逻辑中加速的功能。SDSoC 编译器将生成准备在目标平台板上运行的所有必备硬件和软件。

系统级的特性描述

以赛灵思软件开发套件(SDK)目前提供的高级软件特性描述为基础,SDSoC 增添了系统级特性描述,用于快速系统(软/ 硬件)性能估算。此外,还能快速生成并探索系统级架构,以实现最佳总体系统性能与功耗。

SDSoC 采用基于PC 采样的非侵入式编译器和标准的GPROF 编译器,能帮助用户配置其自身软件应用,以识别占用时间最多且适用于硬件加速的功能。

此外,SDSoC 还增添了快速系统(软/ 硬件)性能和器件利用率估算功能,能够迅速完成系统级架构探索,以实现最佳性能、资源利用率和功耗。用户可在可编程逻辑中设定待加速的功能,而且SDSoC 还能调用C/C++ 代码来报告软件周期、硬件周期、数据传输估算、总体应用加速以及硬件资源利用率等情况。

充分利用基于平台的性能估算流程,软件开发人员能够在数分钟内迅速估算出将一项或多项软件功能转移到硬件中用于加速所产生的性能影响,而实际的硬件生成则需要一小时甚至更长时间。

在目标平台上,SDSoC 使用由ARM CPU 提供的性能计数器,同时自动插入AXI 性能监控器(APM)到可编程逻辑中以采集硬件性能数据,可为缓存、存储器、软件加速器和总线利用率提供自动性能测量。运行在平台上的软件可采集性能数据,SDSoC 就使用该数据帮助识别系统中的性能瓶颈。这种快速的性能反馈能实现最佳代码分区,以满足系统级性能和功耗需求,同时将开发流程缩短数周时间。

物联网 SoC FPGA PSoC ARM 赛灵思 硬件工程师 VHDL Verilog 嵌入式 Linux 总线 相关文章:

- 采用Altera 10代FPGA实现低延时小尺寸设计(06-09)

- 为何使用Zynq SoC可以让企业产品利润激增?(09-15)

- 零基础学FPGA (一) 关于我和FPGA(01-14)

- 赛灵思最新发布的UltraScale+16nm系列FPGA、3D IC和MPSoC介绍(03-04)

- Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势(04-13)

- Xilinx 客户塑造美好的未来(09-07)