利用FPGA实现UART的设计

时间:07-25

来源:互联网

点击:

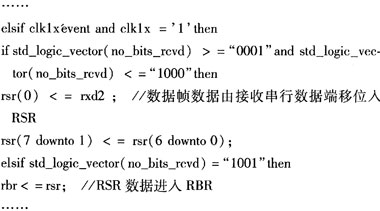

接受器功能仿真结果图略。串行输入RXD为0010101101,每一位占16个时钟周期,一旦检测到输入RXD为0,计数器开始计数,开始接收数据,接收完毕,标志位变为高电平。仿真结果证明了接收模块的正确性。

3.3 波特率发生器的设计

UART的接收和发送是按照相同的波特率进行收发的。波特率发生器产生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,目的是为在接收时进行精确地采样,以提出异步的串行数据。根据给定的晶振时钟和要求的波特率算出波特率分频数。实现的部分VHDL程序如下:

波特率功能仿真结果图略。输入频率为20 MHz,波形周期为50 ns,20 MHz/(9 600 bit/s×16 bit)=130,由仿真结果可知输出波形的半个周期为65倍的输入时钟周期,从而证明了波特率产生器模块的正确性。

4 上位机程序设计

本文使用VB 6.0进行上位机程序的设计,实现PC与FPGA的串行通信。下面是1个上位机收发测试通信程序的设计过程,通过该程序可以与FPGA进行串行通信。波特率默认值是“9600,N,8,1”,其意为所使用的通信端口是以9 600 bit/s的速度传输,不作字符校验,每次的数据是8位,而停止位是1位。波特率(单位为bit/s)可为110、300、600、1200、2400、9 600、14 400、19 200、28 800。校验位为:E偶校验,N无校验,O奇校验,S空白。正确的数据位值有:4、5、6、7、8(默认值)。正确的停止位值有:1(默认值)、1.5、2。

将UART的程序编译、仿真后,下载到FPGA的EPlK30TC144-3芯片上。引入20 MHz的晶振频率;发送使能端和复位端分别接一个开关;状态输出标志TRE和DATA-READTY分别接一个二极管,指示状态;设置波特率为“9 800,N,8,1”。串行数据帧的格式为:起始位0,8位数据位,无校验位,1位停止位。将UART的串行发送、接收端口分别与计算机的RS-232的串行接收、发送端口连接,以便与PC机进行串行通信;并行输入DIN接入并行输出DOUT;连好线后,执行发送测试程序。

5 结束语

在实现FPGA与PC的串行通信中,将程序下载到芯片中验证设计的正确性,目前还没有更好的工具可以在下载后实时地对FPGA的工作情况和数据进行分析。通过串行通信,可以向FPGA发控制命令让其执行相应的操作,同时把需要的数据通过串口发到PC上进行相应的数据处理和分析,以此来判断FPGA是否按设计要求工作。本文以UART为重点讨论了FP-GA与上位机串行通信的实现方法。采用高级语言VB实现了上位机与FPGA的通信。

收发器 EDA 电子 自动化 FPGA CPLD 集成电路 VHDL 仿真 二极管 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 选择合适的FPGA千兆位收发器至关重要(10-28)

- 基于FPGA的高速图像采集系统设计(03-30)

- FPGA高速收发器设计原则(03-11)

- 基于CPLD的USB总线的隔离接口实现(04-08)

- 基于太空级Virtex FPGA的灵活高性能计算平台(04-08)