基于CPLD的USB总线的隔离接口实现

时间:04-08

来源:互联网

点击:

1 引言

大容量数据的高速传输是存储技术的研究的热点技术,而在工业环境的数据传输中抗干扰技术以及医疗设备对人身的安全也是目前研究的热门课题,USB(Universal Serial Bus)是 “通用串行总线”。它是一种应用在 PC领域的接口技术。其主要优点是:可以热插拔、携带方便、标准统一,因而得到了广泛的应用。 USB用于测试与测量应用的优势很多,使用 USB接口的设备也与日俱增,例如数码相机、扫描仪、图像设备、医疗设备、打印机等等。在工业环境自动化程度较高的现场,医疗设备对人体信息的提取和诊断,大量信息数据的获取与存储往往应用快速的 USB接口来实现,而目前的 USB接口对工业干扰非常敏感,在医疗上对人身安全存在隐患,USB的隔离应用是基于 PC平台的医疗设备和具有很大地电位差的工业应用。本文提出基于 CPLD的 USB隔离技术,实现了 USB总线的可靠安全通信,在工业现场和医疗设备通信接口中发挥着重要作用。

2 系统硬件构成及工作原理

全速(12Mbps) USB连接的光隔离,12Mbps的速度可满足一般数据传输的带宽要求,设计中使用廉价耦合器,支持足够的数据传输速率。 USB连接器包含四条线:2条用于电源供电(VBUS和 GND),2条用于 USB数据传输(D+和 D-)。VBUS提供 5V电源,电流可达 500mA。D+和 D-为双向信号线,信号传输速率为 12Mbps (每位 83ns)。D+和 D-信号电平为 3.3V。图1所示隔离 USB接口组成框图,系统主要由 USB收发器 SP5301、光藕电路、主控芯片 CPLD、USB四口 HUB电路 TUSB2046B、电源隔离五部分构成。

图1四口光耦USB接口组成框图

隔离系统的工作原理:差分信号是以半双工的形式实现的,就是说,数据线的任何一部分都可以传送和接收数据,但是在任意时刻只能进行发送或者只能进行接收,两者不能同时进行。半双工实现要求驱动器在不传送数据时进入高阻抗状态。基于此原理,利用 CPLD的控制能力,使其处于上下游的接收状态,一旦检测到一方有信息包到来,立即进行隔离通路的切换,完成信号隔离通过,且保证信号的完整性。

工作过程:外电源接口上电,通过稳压电路提供 5V、3V电压,分别给 CPLD的 I/O口, CPLD核、下游藕合电路、 USB收发器、四口 HUB电路提供电源。CPLD完成复位后,产生控制光耦信号,使上游口上电(由上位机 USB接口提供,节省上位机电源)。 CPLD处于上下游接收状态,当上游差分信号到达 USB收发器后,收发器将差分信号转换为 VP、VM、 RESO三个信号,经光电耦合电路后进入 CPLD检测、处理、切换,再经下游 USB收发器转换为差分信号,送入四口 HUB电路解析处理。反之亦然。

3 系统的软件设计与实现

CPLD是整个系统的控制核心,软件的设计好坏关系到整个系统的稳定性和可靠性。CPLD采用 XILINX公司的 XC95144XL,具有集成度高、可靠性好及工作速度快等优点,开发软件功能强大、灵活易用、升级方便。考虑到 USB信号速度高,要求切换快,便于升级,功耗低,综合各种因素选用该芯片。CPLD的主要功能是: 1)对 50MHZ的时钟信号进行分频,产生系统所需的各种时钟信号;2)为电源的上电顺序提供监测和控制信号; 3)实时判断信息包并及时为 USB收发器提供转换控制信号;4)为 TUSB2046B提供复位信号,监测四口 HUB的 Suspend信号并产生复位信号为上游设备; CPLD控制逻辑状态转换图如图 2所示,系统上电后,CPLD初始化,并为 TUSB2046B产生足够的复位信号,使其正常稳定工作,然后使自己处于上下游接收状态,若上游有信息包,则立即转换下游处于发送状态,让包信号完全通过,包结束时,又回到上下游接收状态。若下游有信息包时,按上述方法上传。

图2 CPLD控制状态转换图

设计实现应用 XILINX公司的集成开发环境 ISE6.3,用 VHDL语言进行描述,采用自顶向下的方法进行设计。考虑到系统的对称性,在此仅画出下游的控制逻辑关系,图 3所示为下游监测与控制的逻辑关系框图,上游没有 down_suspend监测和复位产生电路,其它完全一致。

图3 CPLD内部软件结构框图

4 仿真结果

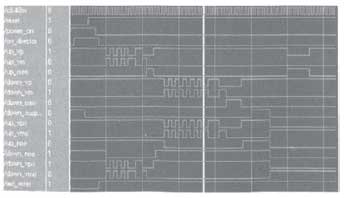

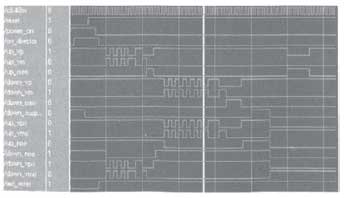

该 USB隔离系统通过 ModelsimXE5.7C进行了波形仿真,仿真波形如图4所示。从波形上可看出:上下游信息包信号都能完整地通过,所需的控制信号及复位信号满足理论设计要求,验证了工作原理的正确性。

5 结论

本设计的主要创新点在于 USB总线的协议的复杂性和快速性为设计实现必须面对许多的挑战,能在分析协议的基础上利用 CPLD解决了 USB总线隔离的问题,巧妙的检测信息包起始、快切换和包结束的难题,克服了传输信息包结束慢上拉与过渡,保证系统的完整性。在各种不同传输信号中,采用各自不同的处理方式,不影响传输线的指标和参数,使系统稳定可靠,该设计在实际的医疗设备对人体测试中达到了预期的效果。实验结果也证明,在后序的网络信息安全的具有生物特征识别功能的 USB研究中提供重要的指导意义。

作者:李广位 来源:《微计算机信息》(嵌入式与SOC)2009年第4-2期

大容量数据的高速传输是存储技术的研究的热点技术,而在工业环境的数据传输中抗干扰技术以及医疗设备对人身的安全也是目前研究的热门课题,USB(Universal Serial Bus)是 “通用串行总线”。它是一种应用在 PC领域的接口技术。其主要优点是:可以热插拔、携带方便、标准统一,因而得到了广泛的应用。 USB用于测试与测量应用的优势很多,使用 USB接口的设备也与日俱增,例如数码相机、扫描仪、图像设备、医疗设备、打印机等等。在工业环境自动化程度较高的现场,医疗设备对人体信息的提取和诊断,大量信息数据的获取与存储往往应用快速的 USB接口来实现,而目前的 USB接口对工业干扰非常敏感,在医疗上对人身安全存在隐患,USB的隔离应用是基于 PC平台的医疗设备和具有很大地电位差的工业应用。本文提出基于 CPLD的 USB隔离技术,实现了 USB总线的可靠安全通信,在工业现场和医疗设备通信接口中发挥着重要作用。

2 系统硬件构成及工作原理

全速(12Mbps) USB连接的光隔离,12Mbps的速度可满足一般数据传输的带宽要求,设计中使用廉价耦合器,支持足够的数据传输速率。 USB连接器包含四条线:2条用于电源供电(VBUS和 GND),2条用于 USB数据传输(D+和 D-)。VBUS提供 5V电源,电流可达 500mA。D+和 D-为双向信号线,信号传输速率为 12Mbps (每位 83ns)。D+和 D-信号电平为 3.3V。图1所示隔离 USB接口组成框图,系统主要由 USB收发器 SP5301、光藕电路、主控芯片 CPLD、USB四口 HUB电路 TUSB2046B、电源隔离五部分构成。

图1四口光耦USB接口组成框图

隔离系统的工作原理:差分信号是以半双工的形式实现的,就是说,数据线的任何一部分都可以传送和接收数据,但是在任意时刻只能进行发送或者只能进行接收,两者不能同时进行。半双工实现要求驱动器在不传送数据时进入高阻抗状态。基于此原理,利用 CPLD的控制能力,使其处于上下游的接收状态,一旦检测到一方有信息包到来,立即进行隔离通路的切换,完成信号隔离通过,且保证信号的完整性。

工作过程:外电源接口上电,通过稳压电路提供 5V、3V电压,分别给 CPLD的 I/O口, CPLD核、下游藕合电路、 USB收发器、四口 HUB电路提供电源。CPLD完成复位后,产生控制光耦信号,使上游口上电(由上位机 USB接口提供,节省上位机电源)。 CPLD处于上下游接收状态,当上游差分信号到达 USB收发器后,收发器将差分信号转换为 VP、VM、 RESO三个信号,经光电耦合电路后进入 CPLD检测、处理、切换,再经下游 USB收发器转换为差分信号,送入四口 HUB电路解析处理。反之亦然。

3 系统的软件设计与实现

CPLD是整个系统的控制核心,软件的设计好坏关系到整个系统的稳定性和可靠性。CPLD采用 XILINX公司的 XC95144XL,具有集成度高、可靠性好及工作速度快等优点,开发软件功能强大、灵活易用、升级方便。考虑到 USB信号速度高,要求切换快,便于升级,功耗低,综合各种因素选用该芯片。CPLD的主要功能是: 1)对 50MHZ的时钟信号进行分频,产生系统所需的各种时钟信号;2)为电源的上电顺序提供监测和控制信号; 3)实时判断信息包并及时为 USB收发器提供转换控制信号;4)为 TUSB2046B提供复位信号,监测四口 HUB的 Suspend信号并产生复位信号为上游设备; CPLD控制逻辑状态转换图如图 2所示,系统上电后,CPLD初始化,并为 TUSB2046B产生足够的复位信号,使其正常稳定工作,然后使自己处于上下游接收状态,若上游有信息包,则立即转换下游处于发送状态,让包信号完全通过,包结束时,又回到上下游接收状态。若下游有信息包时,按上述方法上传。

图2 CPLD控制状态转换图

设计实现应用 XILINX公司的集成开发环境 ISE6.3,用 VHDL语言进行描述,采用自顶向下的方法进行设计。考虑到系统的对称性,在此仅画出下游的控制逻辑关系,图 3所示为下游监测与控制的逻辑关系框图,上游没有 down_suspend监测和复位产生电路,其它完全一致。

图3 CPLD内部软件结构框图

4 仿真结果

该 USB隔离系统通过 ModelsimXE5.7C进行了波形仿真,仿真波形如图4所示。从波形上可看出:上下游信息包信号都能完整地通过,所需的控制信号及复位信号满足理论设计要求,验证了工作原理的正确性。

5 结论

本设计的主要创新点在于 USB总线的协议的复杂性和快速性为设计实现必须面对许多的挑战,能在分析协议的基础上利用 CPLD解决了 USB总线隔离的问题,巧妙的检测信息包起始、快切换和包结束的难题,克服了传输信息包结束慢上拉与过渡,保证系统的完整性。在各种不同传输信号中,采用各自不同的处理方式,不影响传输线的指标和参数,使系统稳定可靠,该设计在实际的医疗设备对人体测试中达到了预期的效果。实验结果也证明,在后序的网络信息安全的具有生物特征识别功能的 USB研究中提供重要的指导意义。

作者:李广位 来源:《微计算机信息》(嵌入式与SOC)2009年第4-2期

USB 总线 自动化 CPLD 连接器 电流 收发器 电路 电压 VHDL 仿真 嵌入式 相关文章:

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- Altera FPGA下载配置(11-11)

- 基于ARM9和CPLD的输入输出系统设计(04-09)

- 基于FPGA的高速图像采集系统设计(03-30)