基于太空级Virtex FPGA的灵活高性能计算平台

时间:04-08

来源:互联网

点击:

目前,天基电子系统开发人员面临的压力越来越大,在项目日程安排越来越紧张且预算一再削减的情况下,他们却需要提供更高的系统性能。然而,天基系统具有一套独特而严格的尺寸、重量和功耗(SWAl?)限制,这对于设计人员来说无疑是一个棘手的问题。

为达到事半功倍的效果,各大公司纷纷采用FPGA等商用成品(COTS)器件。从SWAP限制、成本与工作效率方面来说,可重构的FPGA所固有的灵活性为天基系统的开发人员提供了巨大的帮助。

充分利用现有工程设计与预算资源的一种方式是创建能部署到多个太空任务中的灵活的有效负载。SEAKR工程公司采用可重构的赛灵思Virtex FPGA创建了灵活的高性能计算平台作为各种天基系统的核心。使用该可重构的汁算(RCC)方法,可在多个太空任务的SWAP、成本与时间限制范围内实现高要求的性能目标。最引人注目的例子包括:SEAKR为美国雷神公司(Raytheon)的先进反应战术效能军用成像光谱仪(Artemis)开发的板载处理器、可编程太空收发器以及目前尚在开发过程中的可编程太空IP调制解调器和猎户座视觉处理器。

应用独立处理器的架构

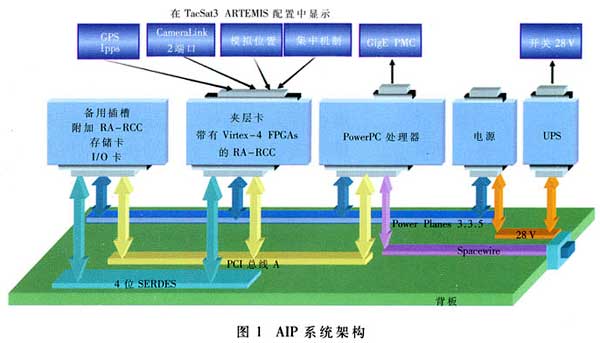

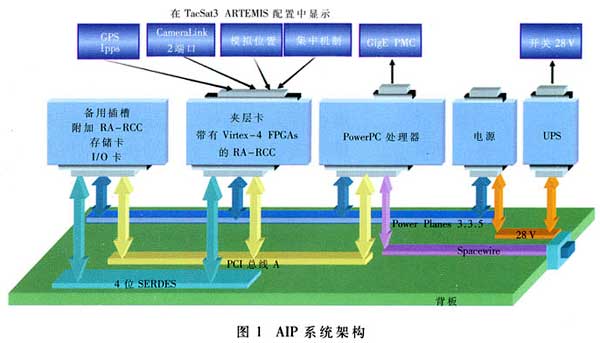

这款全新平台称为应用独立处理器(AIP),在灵活、可扩展的架构中集成了一系列标量处理器与RCC,可支持开放式标准,如图1所示。由于该处理器具有灵活的I/O架构,可以?昆搭各种板卡以创建最适合应用要求的不同配置,称之为专门任务功能。AIP利用赛灵思基于SRAM的FPGA的独特功能,允许在轨重构,从而获得更高的灵活性与SWAP优势。Ail?还支持各种抗单粒子效应(SEE)辐射技术,确保在不同轨道中都能够可靠地进行操作。

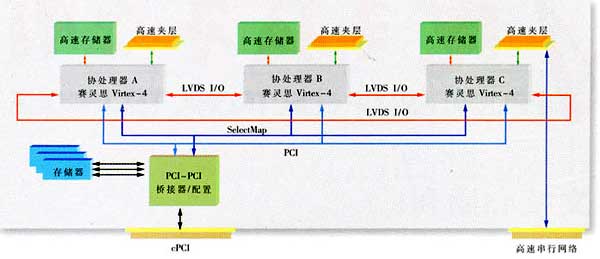

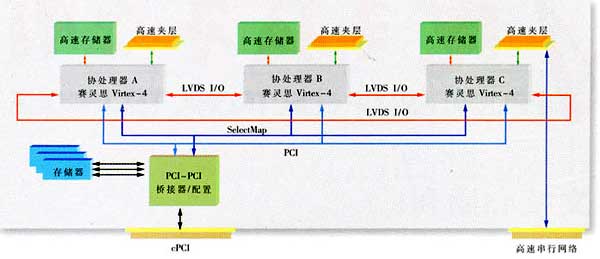

AIP系统架构的核心是一块可重构的计算机板卡,其上包括3个Virtex-4 FPGA,如图2所示。SEAKR对目前可用的组件进行了调研,结果表明Virtex FPGA是惟一能达到性能目标并具有航天飞行特性要求的设备。针对要求最苛刻的应用,赛灵思提供了Virtex-4QV太空级设备。这些太空级FPGA 采用了与商用级FPGA相同的架构,但经过特殊处理和筛选以达到Q类与V类要求。

ViHex-4 FPGA通过与顺序处理器协调工作,可充当协处理器以加速关键处理密集型任务的进展。三重FPGA板的架构具有高度的灵活性,可满足不同任务的独特需求。例如,在抗SEE技术中使用3个FPGA,可满足该技术对组件级冗余性的要求;多个设备间共享一个大型协处理器并使用环形总线通过LVDS接口连接3个 FPGA,可实现设备间的高速通信。采用扩展的6U外形,板卡上将有2个连接器用于板卡间通信:一个用于CompactPCI背板,另一个用于高速串行网络。

每个FPGA都可直接访问RCC板上的专用高速存储器以及支持通过高速夹层卡进行扩展与定制的连接器。使用此架构,可以利用特定I/O、存储器、模拟电路甚至附加逻辑来扩展RCC板的功能。特定应用中的抗SEE辐射架构的组件夹层卡,通过3个连接器与RCC板连接起来,每个连接器可提供170 LVDS I/O。

将特定任务的功能模块移动到夹层卡,可以在多种独特应用中使用相同的基于FPGA的处理卡。该通用架构有助于降低项目风险、减少成本并缩短时间。

FPGA中的抗辐射效应

基于SRAM的配置电路在受到辐射时极易发生翻转,因此在太空中飞行的基于FPGA的可重构系统需要给予特别考虑,以确保其在高辐射环境中可靠运行。首先要考虑组件的选择。除了工业和军事温度级选项外,赛灵思还提供V级Virtex-4与Virtex-5 FPGA,这些FPGA经过特殊处理,可以防止因辐射而导致的闭锁现象,保证总剂量辐射效应下的性能。这些器件还能经受中子和质子i七束的进一步锤炼,可靠地预测出特定轨道上单粒子翻转(SEU)及单粒子功能中断的频率。此数据可指导工程师选择适用于应用与轨道的抗翻转方案。

可重构FPGA的抗翻转功能一般需要组合使用硬件三重冗余与配置存储器清除。硬件三重冗余包括三重关键电路,即使在某一组件发生辐射引发的翻转后也能确保连续运行。此外,它还增加了一个表决电路,该电路将来自3个逻辑分支的、信号进行比较并拒绝因翻转而产生的无效信号。

设计人员可从一系列方案中进行选择,以满足系统性能与可用性要求。其中一种方法是使用冗余FPGA与一个抗辐射的外部表决电路。另一种方法是设备级抗辐射,即在一个FPGA中配置三重关键任务逻辑并使用相关联的表决电路。传统上,工程师手动实现三模冗余(TMR)设计方法。现在,赛灵思提供了专门的设计工具,可在FPGA内自动实现,FMR。选择抗辐射方案时,会受到一些因素的影响,比如目标电路的尺寸、选定轨道中的辐射级别及电路的运行时间要求等。

存储器清除的基本概念是比累计翻转次数更频繁地重写配置存储器。设计人员可从一系列存储器清除方法中进行选择,以适应不同的翻转频率与运行时间要求。最简单的方法就是将完整比特流重新加载到配置存储器中。该方法开销低,但要求电路至少在1个配置周期内保持不工作。对于在运行时间方面要求更严格、翻转率更高或同时存在这2种情况的应用,还可采用更高级的方法。例如充分利用VirtexFPGA的部分重构功能,包括检测存储器翻转然后只重构存储器阵列的选定子集的电路。

为达到事半功倍的效果,各大公司纷纷采用FPGA等商用成品(COTS)器件。从SWAP限制、成本与工作效率方面来说,可重构的FPGA所固有的灵活性为天基系统的开发人员提供了巨大的帮助。

充分利用现有工程设计与预算资源的一种方式是创建能部署到多个太空任务中的灵活的有效负载。SEAKR工程公司采用可重构的赛灵思Virtex FPGA创建了灵活的高性能计算平台作为各种天基系统的核心。使用该可重构的汁算(RCC)方法,可在多个太空任务的SWAP、成本与时间限制范围内实现高要求的性能目标。最引人注目的例子包括:SEAKR为美国雷神公司(Raytheon)的先进反应战术效能军用成像光谱仪(Artemis)开发的板载处理器、可编程太空收发器以及目前尚在开发过程中的可编程太空IP调制解调器和猎户座视觉处理器。

应用独立处理器的架构

这款全新平台称为应用独立处理器(AIP),在灵活、可扩展的架构中集成了一系列标量处理器与RCC,可支持开放式标准,如图1所示。由于该处理器具有灵活的I/O架构,可以?昆搭各种板卡以创建最适合应用要求的不同配置,称之为专门任务功能。AIP利用赛灵思基于SRAM的FPGA的独特功能,允许在轨重构,从而获得更高的灵活性与SWAP优势。Ail?还支持各种抗单粒子效应(SEE)辐射技术,确保在不同轨道中都能够可靠地进行操作。

AIP系统架构的核心是一块可重构的计算机板卡,其上包括3个Virtex-4 FPGA,如图2所示。SEAKR对目前可用的组件进行了调研,结果表明Virtex FPGA是惟一能达到性能目标并具有航天飞行特性要求的设备。针对要求最苛刻的应用,赛灵思提供了Virtex-4QV太空级设备。这些太空级FPGA 采用了与商用级FPGA相同的架构,但经过特殊处理和筛选以达到Q类与V类要求。

ViHex-4 FPGA通过与顺序处理器协调工作,可充当协处理器以加速关键处理密集型任务的进展。三重FPGA板的架构具有高度的灵活性,可满足不同任务的独特需求。例如,在抗SEE技术中使用3个FPGA,可满足该技术对组件级冗余性的要求;多个设备间共享一个大型协处理器并使用环形总线通过LVDS接口连接3个 FPGA,可实现设备间的高速通信。采用扩展的6U外形,板卡上将有2个连接器用于板卡间通信:一个用于CompactPCI背板,另一个用于高速串行网络。

每个FPGA都可直接访问RCC板上的专用高速存储器以及支持通过高速夹层卡进行扩展与定制的连接器。使用此架构,可以利用特定I/O、存储器、模拟电路甚至附加逻辑来扩展RCC板的功能。特定应用中的抗SEE辐射架构的组件夹层卡,通过3个连接器与RCC板连接起来,每个连接器可提供170 LVDS I/O。

将特定任务的功能模块移动到夹层卡,可以在多种独特应用中使用相同的基于FPGA的处理卡。该通用架构有助于降低项目风险、减少成本并缩短时间。

FPGA中的抗辐射效应

基于SRAM的配置电路在受到辐射时极易发生翻转,因此在太空中飞行的基于FPGA的可重构系统需要给予特别考虑,以确保其在高辐射环境中可靠运行。首先要考虑组件的选择。除了工业和军事温度级选项外,赛灵思还提供V级Virtex-4与Virtex-5 FPGA,这些FPGA经过特殊处理,可以防止因辐射而导致的闭锁现象,保证总剂量辐射效应下的性能。这些器件还能经受中子和质子i七束的进一步锤炼,可靠地预测出特定轨道上单粒子翻转(SEU)及单粒子功能中断的频率。此数据可指导工程师选择适用于应用与轨道的抗翻转方案。

可重构FPGA的抗翻转功能一般需要组合使用硬件三重冗余与配置存储器清除。硬件三重冗余包括三重关键电路,即使在某一组件发生辐射引发的翻转后也能确保连续运行。此外,它还增加了一个表决电路,该电路将来自3个逻辑分支的、信号进行比较并拒绝因翻转而产生的无效信号。

设计人员可从一系列方案中进行选择,以满足系统性能与可用性要求。其中一种方法是使用冗余FPGA与一个抗辐射的外部表决电路。另一种方法是设备级抗辐射,即在一个FPGA中配置三重关键任务逻辑并使用相关联的表决电路。传统上,工程师手动实现三模冗余(TMR)设计方法。现在,赛灵思提供了专门的设计工具,可在FPGA内自动实现,FMR。选择抗辐射方案时,会受到一些因素的影响,比如目标电路的尺寸、选定轨道中的辐射级别及电路的运行时间要求等。

存储器清除的基本概念是比累计翻转次数更频繁地重写配置存储器。设计人员可从一系列存储器清除方法中进行选择,以适应不同的翻转频率与运行时间要求。最简单的方法就是将完整比特流重新加载到配置存储器中。该方法开销低,但要求电路至少在1个配置周期内保持不工作。对于在运行时间方面要求更严格、翻转率更高或同时存在这2种情况的应用,还可采用更高级的方法。例如充分利用VirtexFPGA的部分重构功能,包括检测存储器翻转然后只重构存储器阵列的选定子集的电路。

电子 FPGA 赛灵思 收发器 总线 连接器 模拟电路 电路 传感器 嵌入式 无线电 电源模块 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)