基于SRAM编程技术的PLD核心可重构电路结构设计

时间:07-23

来源:互联网

点击:

八十年代中期,高密度可编程逻辑器件(Programmable Logic Device,简称PLD)的出现开辟了一种数字逻辑电路实现的新方式。高密度的PLD可以分成两大类:复杂可编程逻辑器件(Complex Programmable Logic Device,简称CPLD)和现场可编程门阵列(Field Programmable GateArray,简称FPGA),主要基于三种编程技术:有限编程次数(一般数百次到上万次)的EEPROM(电可擦除只读存储器)、无限编程次数的SRAM(静态随机存储器)和仅可编程一次的Antifuse(反熔丝)。当前,主流的CPLD都是采用基于EEPROM的乘积项(Product Term,简称P-Term)结构,而主流的FPGA则采用基于SRAM的查找表(Look-up Table,简称LUT)结构和基于Antifuse的多路开关单元结构。其中,基于SRAM的FPGA由于可以在系统中重构甚至动态重构,所以应用灵活性最大。

近十年来兴起的可重构技术起源于FPGA可编程结构的思想。该技术在应用中可以获得很好的速度和灵活性之间的折衷,填补了传统的软、硬件应用实现方案之间的空白。可重构技术是指利用具有硬件可重构结构的电路构建系统来满足较宽范围应用的实现技术。采用FPGA作为重构系统的核心既可以大大缩短系统开发时间,又可以获得很高的灵活性以节约资源。FPGA中含有大量的触发器(多达上千个)和结构灵活的LUT,适合实现细颗粒度的且基于流水线的通用计算。对于可重构多总线控制和网络中数据包相关的不同协议处理等应用,需要时时变换的译码和控制。重构系统在完成上述应用时,需要可以动态重构的复杂状态机和译码电路。由于这些电路中组合逻辑复杂且输入数目大而触发器很少,因此,用FPGA实现会造成单元中触发器大量浪费,而且利用多个LUT的级连实现大输入的组合逻辑,会使性能大大降低,难以满足速度上的要求。

CPLD的结构非常适于实现上述逻辑功能。但是,CPLD的EEPROM编程速度低且编程次数有限又不适合要求快速频繁重构的动态重构系统的应用。

显然,设计基于SRAM编程技术的CPLD可以很好解决上述应用问题。CPLD的设计和实现的关键问题是核心可编程电路结构的实现。因此,本文主要探讨针对CPLD的核心可编程结构,如何设计具有相似功能且基于SRAM编程技术的电路结构,从而更好满足动态重构系统中实现复杂状态机和译码电路的应用。

CPLD的核心可编程结构介绍

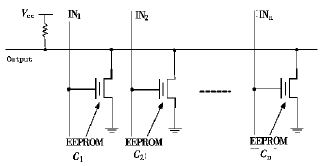

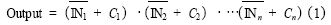

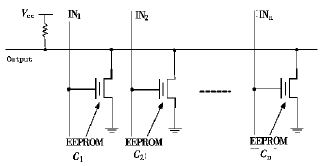

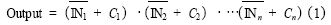

CPLD由若干宏单元和可编程互连线构成。每个宏单元包括5个乘积项、1个异或门、1个5输入或门和1个触发器。乘积项是宏单元的核心可编程结构,可以灵活实现大输入数目宽与门功能。如图1a所示,P-Term是一个由EEPROM晶体管构成的阵列。该阵列中每个EEPROM晶体管相当于一个可编程开关,编程之后,处于“开”状态的EEP2ROM晶体管同普通晶体管一样,受栅极输入控制充当宽与门的下拉开关,而处于“关”状态的EEP2ROM晶体管是断路,栅极的输入对宽与门无贡献。这样,P-Term所实现的逻辑功能可由式(1)给出:

(a) 基于EEPROM的可编程宽与门结构

(b) MAX7000中的PIA可编程结构

图1 电路结构图

式(1)中,C1~Cn对应图1(a)中的n个EEPROM晶体管编程后所处的状态。当第i(i=1~n)个位置的EEPROM晶体管开时,Ci为0,反之,Ci为1。当前,主流的CPLD全部采用这种结构,比如Altera公司的MAX7000系列和MAX9000系列、Xilinx公司的XC9500系列以及Lattice公司的ispLSI系列等。

可编程互连线是CPLD中另一个核心可编程结构。该结构是包含大量可编程开关的互连网络,提供芯片的I/O引脚和宏单元的输入输出之间的灵活互连。具有固定的延时是CPLD中可编程互连线的最显著特点。不同于FPGA的分段式可编程互连方式,CPLD结构采用全局式的可编程互连网络来集中分配互连线资源,这样可以使连线路径的起点到终点延时固定。而FPGA中连线路径的起点到终点之间经过的分段连线数目不固定,因此延时也是不固定的。相比之下,CPLD在实现较复杂的组合逻辑时可以消除信号之间的歪斜,更容易消除竞争冒险现象。目前,主流的CPLD全部采用连续式互连线结构,比如MAX7000中的PIA结构和XC9500中的FastCONNECT结构。图1(b)给出了MAX7000中PIA的逻辑结构。该结构中,每个编程节点的EEPROM晶体管控制2输入与门的1个输入端来决定另一输入端信号的取舍。

综上所述,CPLD的核心可编程结构是P-Term和具有固定延时的可编程互连线结构。

基于SRAM编程技术的PLD电路结构设计

针对CPLD的核心可编程结构——P-Term和具有固定延时的可编程互连线,设计了基于SRAM编程技术的新电路结构,下面做详细介绍。

近十年来兴起的可重构技术起源于FPGA可编程结构的思想。该技术在应用中可以获得很好的速度和灵活性之间的折衷,填补了传统的软、硬件应用实现方案之间的空白。可重构技术是指利用具有硬件可重构结构的电路构建系统来满足较宽范围应用的实现技术。采用FPGA作为重构系统的核心既可以大大缩短系统开发时间,又可以获得很高的灵活性以节约资源。FPGA中含有大量的触发器(多达上千个)和结构灵活的LUT,适合实现细颗粒度的且基于流水线的通用计算。对于可重构多总线控制和网络中数据包相关的不同协议处理等应用,需要时时变换的译码和控制。重构系统在完成上述应用时,需要可以动态重构的复杂状态机和译码电路。由于这些电路中组合逻辑复杂且输入数目大而触发器很少,因此,用FPGA实现会造成单元中触发器大量浪费,而且利用多个LUT的级连实现大输入的组合逻辑,会使性能大大降低,难以满足速度上的要求。

CPLD的结构非常适于实现上述逻辑功能。但是,CPLD的EEPROM编程速度低且编程次数有限又不适合要求快速频繁重构的动态重构系统的应用。

显然,设计基于SRAM编程技术的CPLD可以很好解决上述应用问题。CPLD的设计和实现的关键问题是核心可编程电路结构的实现。因此,本文主要探讨针对CPLD的核心可编程结构,如何设计具有相似功能且基于SRAM编程技术的电路结构,从而更好满足动态重构系统中实现复杂状态机和译码电路的应用。

CPLD的核心可编程结构介绍

CPLD由若干宏单元和可编程互连线构成。每个宏单元包括5个乘积项、1个异或门、1个5输入或门和1个触发器。乘积项是宏单元的核心可编程结构,可以灵活实现大输入数目宽与门功能。如图1a所示,P-Term是一个由EEPROM晶体管构成的阵列。该阵列中每个EEPROM晶体管相当于一个可编程开关,编程之后,处于“开”状态的EEP2ROM晶体管同普通晶体管一样,受栅极输入控制充当宽与门的下拉开关,而处于“关”状态的EEP2ROM晶体管是断路,栅极的输入对宽与门无贡献。这样,P-Term所实现的逻辑功能可由式(1)给出:

(a) 基于EEPROM的可编程宽与门结构

(b) MAX7000中的PIA可编程结构

图1 电路结构图

式(1)中,C1~Cn对应图1(a)中的n个EEPROM晶体管编程后所处的状态。当第i(i=1~n)个位置的EEPROM晶体管开时,Ci为0,反之,Ci为1。当前,主流的CPLD全部采用这种结构,比如Altera公司的MAX7000系列和MAX9000系列、Xilinx公司的XC9500系列以及Lattice公司的ispLSI系列等。

可编程互连线是CPLD中另一个核心可编程结构。该结构是包含大量可编程开关的互连网络,提供芯片的I/O引脚和宏单元的输入输出之间的灵活互连。具有固定的延时是CPLD中可编程互连线的最显著特点。不同于FPGA的分段式可编程互连方式,CPLD结构采用全局式的可编程互连网络来集中分配互连线资源,这样可以使连线路径的起点到终点延时固定。而FPGA中连线路径的起点到终点之间经过的分段连线数目不固定,因此延时也是不固定的。相比之下,CPLD在实现较复杂的组合逻辑时可以消除信号之间的歪斜,更容易消除竞争冒险现象。目前,主流的CPLD全部采用连续式互连线结构,比如MAX7000中的PIA结构和XC9500中的FastCONNECT结构。图1(b)给出了MAX7000中PIA的逻辑结构。该结构中,每个编程节点的EEPROM晶体管控制2输入与门的1个输入端来决定另一输入端信号的取舍。

综上所述,CPLD的核心可编程结构是P-Term和具有固定延时的可编程互连线结构。

基于SRAM编程技术的PLD电路结构设计

针对CPLD的核心可编程结构——P-Term和具有固定延时的可编程互连线,设计了基于SRAM编程技术的新电路结构,下面做详细介绍。

电路 CPLD FPGA 总线 Altera Xilinx 仿真 CMOS 电阻 电流 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)