基于SRAM编程技术的PLD核心可重构电路结构设计

时间:07-23

来源:互联网

点击:

- SRAM编程单元的电路结构设计

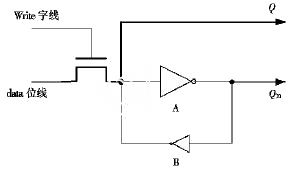

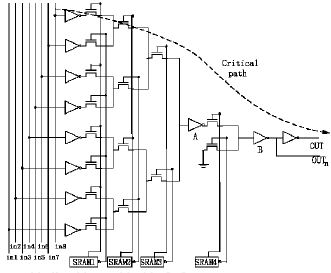

基于SRAM的编程技术是将PLD的每一位配置数据相应存储在SRAM单元中。如图2a所示,

(a) SRAM编程单元结构

(b) SRAM单元的Hspice仿真结果

图2 电路结构与仿真结果图

本设计采用5管单元的SRAM结构。该结构由2个CMOS反向器组成环路形成双稳态。不同于普通的SRAM,PLD的SRAM编程单元不需要读出功能,仅需写入的字线和位线。图2(a)中的输出信号Q和Qn直接控制晶体管开或关来完成可编程的功能。这种结构设计的关键之处在于选择适当的晶体管尺寸以保证当字线选通位线时,data信号的正常逻辑值可以改变单元的状态。因此,本设计确定字线控制的晶体管和反向器A具有较强的驱动能力,而反向器B的驱动能力较弱,适当调节晶体管的宽长比,以保证编程数据的快速写入。图2(b)给出了本设计中SRAM单元的Hspice仿真结果(基于2.5V、0.25μmCMOS工艺库的模型参数,后面的仿真结果都是基于这个工艺库),图中a和b两条曲线分别代表信号Q和Qn。图2(b)中的(1)和(2)图分别表示Q和Qn在写入高电平(单元中存储的是低电平)和低电平(单元中存储的是高电平)时的变化情况。从图中可以看出,写入的最大延时约为650ps,发生在写入高电平时。这样,该结构完全可以满足高速重构的配置速度要求。

基于SRAM编程技术的P-Term电路结构设计

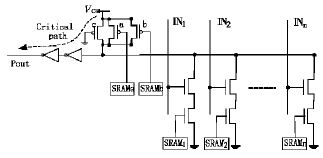

基于SRAM的P-Term结构的设计核心是可编程宽与门的结构设计,即设计能够实现式(1)功能的结构。理论上,实现式(1)功能的结构有很多,比如采用静态CMOS逻辑门或传输门构成的逻辑,但是P-Term的输入数目巨大,可达88个输入,这样,采用上述结构在电路面积和性能上根本无法接受。而采用类NMOS电路结构在面积和性能上可以获得很好的效果,但是这种电路在输出低电平时存在电源到地的直流通路,存在静态功耗,而且输出低电平不是0,而决定于上拉和下拉倒通电阻的分压比。可见,这种电路的设计重点在于上拉结构的设计。本文设计的基于SRAM的可编程宽与门电路结构就是以类NMOS结构为基础的,采用可编程上拉结构控制功耗和性能的折衷。

本文设计的电路结构如图3(a)所示,输入个数n=88。采用NMOS晶体管构成下拉网络,对应每一个输入的下拉结构是输入控制的NMOS管串联SRAM控制的NMOS管。SRAM中的编程数据控制对应晶体管的开关来决定相应的与门输入的取舍。输出采用2个反向器构成缓冲,解决类NMOS电路输出低电平不是0的问题。可编程的上拉结构由a、b、c三个PMOS管并联构成,其中PMOS管c常通,a和b受SRAM编程控制开或关。这样,该结构在SRAMa和SRAMb的编程控制下,具有三种不同的速度和功耗模式:高速高功耗(PMOS管a和b都通)、中速而功耗中等(a通而b不通)和低速低功耗(a、b都不通)。由于三个PMOS管的导通电阻要比下拉NMOS管的大很多,本结构的关键路径是图中虚线表示的高电平充电路径。

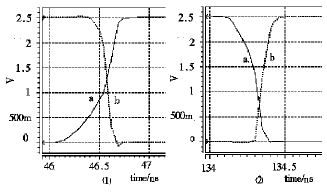

在上述三种工作模式下,关键路径的Hspice仿真结果如图3(b)所示,其中(1)、(2)和(3)图分别表示三种模式下,输入信号由高电平到低电平的变化导致输出Pout由低电平到高电平的变化情况,曲线a为输入信号,b为输出信号Pout。在高速模式下,关键路径延时约为1 .2ns,但电源到地的静态电流也达到了56μA;在中速模式下,关键路径延时约为2.2ns,静态电流为29μA;在低功耗模式下,关键路径延时约为4ns,静态电流仅为14μA。

(a) 基于SRAM的可编程宽与门电路结构

(b) 宽与门关键路径的Hspice仿真结果

图3 电路结构与仿真结果图

基于SRAM编程技术的可编程互连线电路结构设计

CPLD中可编程互连线的作用是集中分配输入信号以固定延时输出到宏单元的输入端(P- Term的输入端)。本文所设计的可编程互连线是由结构完全相同的可编程连线单元组成的二维阵列。可编程连线单元之间不存在互连关系,每个单元的输入信号直接来自于输入总线,输出信号直接到宏单元,这样可以保证延时固定。因此,这种结构的设计实质上是可编程连线单元的结构设计。

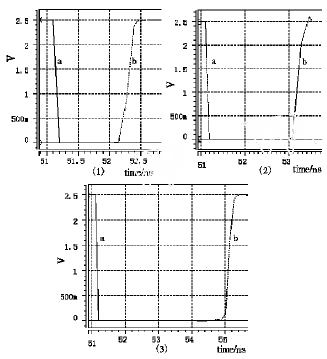

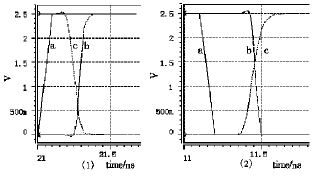

本文设计的基于SRAM的可编程连线单元结构如图4(a)所示。该结构的作用是在8条输入线中选择1条或者都不选而仅选择低电平输出,然后将选择的输出变成正反两个信号输出到宏单元中P-Term的输入端。核心结构是SRAM控制的多路选择器,其中的SRAM编程控制位SRAM1~SRAM3

(a) 基于SRAM的可编程互连单元电路结构

(b) 可编程互连单元关键路径的Hspice仿真结果

图4 电路结构与仿真结果图

控制多路选择器实现8选1的连线状态,而SRAM4控制开关管实现输出低电平。本设计仅用单NMOS管构成多路选择器,相对于采用传输门的情况,每个开关减少了1个晶体管。但是,NMOS传送高电平存在阈值损耗,因此,在选择适当晶体管尺寸的同时,在第3、4级开关处分别加了反向器A和B,保证输出高电平的幅值和足够的驱动能力。可编程互连线延时对PLD的速度起决定性作用。图4 (a)中的虚线是本结构的关键路径,图4(b)给出了关键路径的Hspice仿真结果,(1)和(2)图分别为输入信号上升和下降引起输出的变化情况,a、b和c三条曲线分别表示输入总线信号、输出的正反信号OUT和OUTn。仿真结果表明,本结构的最大延时仅为300ps。

特别指出,本结构仅用了4bitSRAM编程就实现了MAX7000的PIA单元中1组开关的功能,而图1(b)中的结构需要8bitEEPROM。这样,本结构同基于EEPROM的结构相比,减少了4bit编程数据,从而使基于本结构的可编程互连线的编程数据减少了50%。编程数据的减少,可以缩短器件配置的时间,提高在重构系统应用中动态重构的效率。

电路 CPLD FPGA 总线 Altera Xilinx 仿真 CMOS 电阻 电流 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)