利用FPGA实现UART的设计

时间:07-25

来源:互联网

点击:

引 言

随着计算机技术的发展和广泛应用,尤其是在工业控制领域的应用越来越广泛,计算机通信显的尤为重要。串行通信虽然使设备之间的连线大为减少,但随之带来串/并转换和位计数等问题,这使串行通信技术比并行通信技术更为复杂。串/并转换可用软件实现,也可用硬件实现。用软件实现串行传送大多采用循环移位指令将一个字节由高位到低位(或低位到高位)一位一位依次传送,这种方法虽然简单但速度慢,而且大量占用CPU的时间,影响系统的性能。更为方便的实现方法是用硬件,目前微处理器串行接口常用的LSI 芯片是UART(通用异步收发器)、USART(通用同步异步收发器)和ACIA(异步通信接口适配器)等。不论是哪一种芯片,它们的一种基本功能是实现串/并转换。正是这些串行接口芯片弥补了串行通信较为复杂这一缺陷。本文应用EDA(电子设计自动化)技术,基于FPGA(现场可编程门阵列)/CPLD(复杂可编程逻辑器件)设计与实现UART。

1 总体设计

整个设计包括两部分:基于FPGA的UART的设计和基于VB6.0的上位机程序设计。UART的设计采用模块化的设计思想,可分为3个模块:FPGA数据发送模块、FPGA波特率发生器控制模块及数据接收模块。上位机程序采用VB 6.0的Mscomm控件,可分为画面设计和功能设计两部分。串口采用标准的RS-232协议,主要参数选择为:波特率9 600 bit/s,8位有效位,无奇偶校验位,1位停止位。

2 UART的结构和帧格式

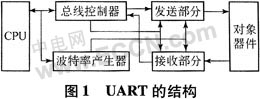

UART主要包括接收器和发送器。从异步接收输入信号SIN接收到的异步信号通过接收器完成串行/并行的转换,形成异步数据帧;发送器将CPU发出的8位数据进行并行/串行转换,从SOUT发送出去。功能包括微处理器接口、TBR(发送缓冲器)、TSR(发送移位寄存器)、帧产生、并转串、RBR(接收缓冲器)、RSR(接收移位寄存器)、帧产生、串转并。UART的结构如图1所示。

UART的帧格式包括线路空闲状态(idle,高电平)、起始位(start bit,低电平)、5位~8位数据位(da-ta bits)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。这种格式是由起始位和停止位来实现字符的同步。UART内部一般有配置寄存器,可以配置数据位数(5位~8位)、是否有校验位和校验的类型、停止位的位数(1,1.5,2位)等设置。

3 UART的设计与实现

UART是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。串行外设使用RS-232-C异步串行接口,一般采用专用集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时不需要使用完整的UART的功能和这些辅助功能,或者使用了FPGA/CPLD,那么就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。

下面分别设计UART的3个模块(发送器、接收器和波特率产生器),并给出其仿真结果。

3.1 发送器设计

UART串行发送器模块框图如图2所示。DIN为8位数据,其余为1位。

从图2的框图可以看出,串行发送器中包含有一个8位THR(发送保持寄存器)和TSR(发送移位寄存)。复位时,引脚TRE为高电平。当数据载入到TSR之后,引脚TRE变为低电平。发送完毕,TRE变为高电平。当侦测到输入WRN变为低电平时,自动使能串行数据发送过程。首先传送1位的起始位(逻辑电平0),同时THR中的数据自动地并行载入到TSR中。然后,定长的数据位从TSR中移出,接着是校验位。最后,产生停止位(逻辑电平1),标志着一帧的结束。串行数据帧将以内部时钟频率的1/16传送。如果THR中内容不空,当一个串行数据帧传送结束后,紧接着发送下一个数据帧。这种自动的流程使得数据帧以背靠背的方式发送,提高了数据传输的带宽。当没有数据发送时,SDO引脚保持高电平。

发送器每隔16个时钟周期输出1位,顺序遵循1位起始位、8位数据位(假定数据位为8位)、1位校验位(可选)、1位停止位。引入发送字符长度和发送次序计数器no_bits_sent,实现的部分VHDL程序如下:

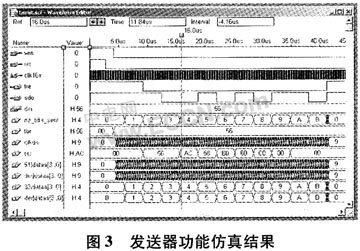

发送器功能仿真结果如图3所示。并行输入DIN十六进制数56,WRN输入由1变为0,肩动发送程序,计数器开始计数,串行输出SDO为0010101101,发送完毕,TRE变为高电平。起始位0,8位数据位,1位停止位,证明了发送模块的正确性。

3.2 接收器设计

UART串行接收器模块框图如图4所示。DOUT为8位数据,其余为1位。接收器包含一个8位RBR和RSR。RBR的状态可以通过引脚DATA_READY米表示。当RBR中的数据有效时,DATA_READY变为高电平,向CPU表明可以取同数据。

本设计只要求实现简单的收发功能,故未设计检错程序,程序在侦测到起始位后,计16个时钟周期,便开始接收数据,移位输入RSR,最后输出数据DOUT。还要输出一个数据接收标志信号标志数据接收完。实现的部分VHDL程序如下:

随着计算机技术的发展和广泛应用,尤其是在工业控制领域的应用越来越广泛,计算机通信显的尤为重要。串行通信虽然使设备之间的连线大为减少,但随之带来串/并转换和位计数等问题,这使串行通信技术比并行通信技术更为复杂。串/并转换可用软件实现,也可用硬件实现。用软件实现串行传送大多采用循环移位指令将一个字节由高位到低位(或低位到高位)一位一位依次传送,这种方法虽然简单但速度慢,而且大量占用CPU的时间,影响系统的性能。更为方便的实现方法是用硬件,目前微处理器串行接口常用的LSI 芯片是UART(通用异步收发器)、USART(通用同步异步收发器)和ACIA(异步通信接口适配器)等。不论是哪一种芯片,它们的一种基本功能是实现串/并转换。正是这些串行接口芯片弥补了串行通信较为复杂这一缺陷。本文应用EDA(电子设计自动化)技术,基于FPGA(现场可编程门阵列)/CPLD(复杂可编程逻辑器件)设计与实现UART。

1 总体设计

整个设计包括两部分:基于FPGA的UART的设计和基于VB6.0的上位机程序设计。UART的设计采用模块化的设计思想,可分为3个模块:FPGA数据发送模块、FPGA波特率发生器控制模块及数据接收模块。上位机程序采用VB 6.0的Mscomm控件,可分为画面设计和功能设计两部分。串口采用标准的RS-232协议,主要参数选择为:波特率9 600 bit/s,8位有效位,无奇偶校验位,1位停止位。

2 UART的结构和帧格式

UART主要包括接收器和发送器。从异步接收输入信号SIN接收到的异步信号通过接收器完成串行/并行的转换,形成异步数据帧;发送器将CPU发出的8位数据进行并行/串行转换,从SOUT发送出去。功能包括微处理器接口、TBR(发送缓冲器)、TSR(发送移位寄存器)、帧产生、并转串、RBR(接收缓冲器)、RSR(接收移位寄存器)、帧产生、串转并。UART的结构如图1所示。

UART的帧格式包括线路空闲状态(idle,高电平)、起始位(start bit,低电平)、5位~8位数据位(da-ta bits)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。这种格式是由起始位和停止位来实现字符的同步。UART内部一般有配置寄存器,可以配置数据位数(5位~8位)、是否有校验位和校验的类型、停止位的位数(1,1.5,2位)等设置。

3 UART的设计与实现

UART是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。串行外设使用RS-232-C异步串行接口,一般采用专用集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时不需要使用完整的UART的功能和这些辅助功能,或者使用了FPGA/CPLD,那么就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。

下面分别设计UART的3个模块(发送器、接收器和波特率产生器),并给出其仿真结果。

3.1 发送器设计

UART串行发送器模块框图如图2所示。DIN为8位数据,其余为1位。

从图2的框图可以看出,串行发送器中包含有一个8位THR(发送保持寄存器)和TSR(发送移位寄存)。复位时,引脚TRE为高电平。当数据载入到TSR之后,引脚TRE变为低电平。发送完毕,TRE变为高电平。当侦测到输入WRN变为低电平时,自动使能串行数据发送过程。首先传送1位的起始位(逻辑电平0),同时THR中的数据自动地并行载入到TSR中。然后,定长的数据位从TSR中移出,接着是校验位。最后,产生停止位(逻辑电平1),标志着一帧的结束。串行数据帧将以内部时钟频率的1/16传送。如果THR中内容不空,当一个串行数据帧传送结束后,紧接着发送下一个数据帧。这种自动的流程使得数据帧以背靠背的方式发送,提高了数据传输的带宽。当没有数据发送时,SDO引脚保持高电平。

发送器每隔16个时钟周期输出1位,顺序遵循1位起始位、8位数据位(假定数据位为8位)、1位校验位(可选)、1位停止位。引入发送字符长度和发送次序计数器no_bits_sent,实现的部分VHDL程序如下:

发送器功能仿真结果如图3所示。并行输入DIN十六进制数56,WRN输入由1变为0,肩动发送程序,计数器开始计数,串行输出SDO为0010101101,发送完毕,TRE变为高电平。起始位0,8位数据位,1位停止位,证明了发送模块的正确性。

3.2 接收器设计

UART串行接收器模块框图如图4所示。DOUT为8位数据,其余为1位。接收器包含一个8位RBR和RSR。RBR的状态可以通过引脚DATA_READY米表示。当RBR中的数据有效时,DATA_READY变为高电平,向CPU表明可以取同数据。

本设计只要求实现简单的收发功能,故未设计检错程序,程序在侦测到起始位后,计16个时钟周期,便开始接收数据,移位输入RSR,最后输出数据DOUT。还要输出一个数据接收标志信号标志数据接收完。实现的部分VHDL程序如下:

收发器 EDA 电子 自动化 FPGA CPLD 集成电路 VHDL 仿真 二极管 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 选择合适的FPGA千兆位收发器至关重要(10-28)

- 基于FPGA的高速图像采集系统设计(03-30)

- FPGA高速收发器设计原则(03-11)

- 基于CPLD的USB总线的隔离接口实现(04-08)

- 基于太空级Virtex FPGA的灵活高性能计算平台(04-08)