一篇文章读懂读透FPGA AXI4 总线协议

时间:08-19

来源:电子发烧友网工程师

点击:

址;②提供对齐的起始地址,使用字节线来表示非对齐的起始地址。

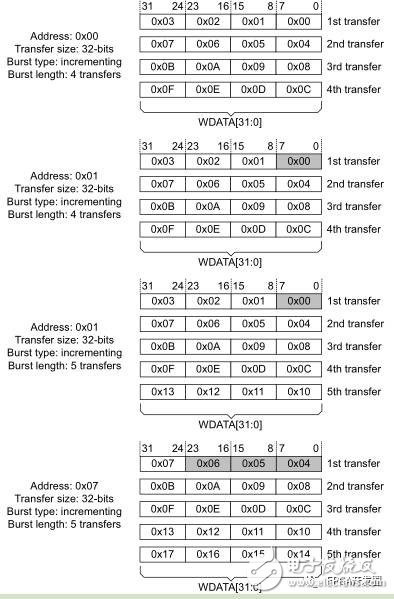

图 3-9 对齐非对齐传输示例1-32bit总线

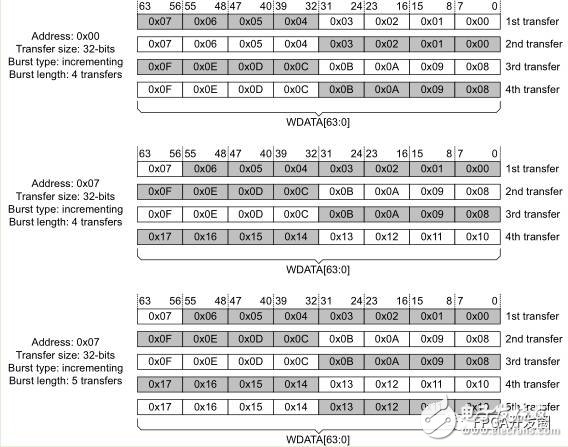

图 3-10 对齐非对齐传输示例2-64bit总线

图 3-11 对齐的回环传输示例

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY(‘b00):正常访问成功

EXOKAY(‘b01):Exclusive 访问成功

SLVERR(‘b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR(‘b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)