一篇文章读懂读透FPGA AXI4 总线协议

| WDATA | 主机 | 写数据 |

| WSTRB | 主机 | 写数据有效的字节线,用来表明哪8bits数据是有效的 |

| WLAST | 主机 | 表明此次传输是最后一个突发传输 |

| WUSER | 主机 | 用户自定义信号 |

| WVALID | 主机 | 写有效,表明此次写有效 |

| WREADY | 从机 | 表明从机可以接收写数据 |

表 2-4 写响应通道信号

| 信号名 | 源 | 描述 |

| BID | 从机 | 写响应ID tag |

| BRESP | 从机 | 写响应,表明写传输的状态 |

| BUSER | 从机 | 用户自定义 |

| BVALID | 从机 | 写响应有效 |

| BREADY | 主机 | 表明主机能够接收写响应 |

表 2-5 读地址通道信号

| 信号名 | 源 | 描述 |

| ARID | 主机 | 读地址ID,用来标志一组写信号 |

| ARADDR | 主机 | 读地址,给出一次写突发传输的读地址 |

| ARLEN | 主机 | 突发长度,给出突发传输的次数 |

| ARSIZE | 主机 | 突发大小,给出每次突发传输的字节数 |

| ARBURST | 主机 | 突发类型 |

| ARLOCK | 主机 | 总线锁信号,可提供操作的原子性 |

| ARCACHE | 主机 | 内存类型,表明一次传输是怎样通过系统的 |

| ARPROT | 主机 | 保护类型,表明一次传输的特权级及安全等级 |

| ARQOS | 主机 | 质量服务QoS |

| ARREGION | 主机 | 区域标志,能实现单一物理接口对应的多个逻辑接口 |

| ARUSER | 主机 | 用户自定义信号 |

| ARVALID | 主机 | 有效信号,表明此通道的地址控制信号有效 |

| ARREADY | 从机 | 表明"从"可以接收地址和对应的控制信号 |

表 2-6 读数据通道信号

| 信号名 | 源 | 描述 |

| RID | 从机 | 读ID tag |

| RDATA | 从机 | 读数据 |

| RRESP | 从机 | 读响应,表明读传输的状态 |

| RLAST | 从机 | 表明读突发的最后一次传输 |

| RUSER | 从机 | 用户自定义 |

| RVALID | 从机 | 表明此通道信号有效 |

| RREADY | 主机 | 表明主机能够接收读数据和响应信息 |

表 2-7 低功耗接口信号

| 信号名 | 源 | 描述 |

| CSYSREQ | 时钟控制器 | 系统退出低功耗请求,此信号从"时钟控制器"到"外设" |

| CSYSACK | 外设 | 退出低功耗状态确认 |

| CACTIVE | 外设 | 外设请求时钟有效 |

3.信号接口要求

3.1时钟复位

时钟

每个AXI组件使用一个时钟信号ACLK,所有输入信号在ACLK上升沿采样,所有输出信号必须在ACLK上升沿后发生。

复位

AXI使用一个低电平有效的复位信号ARESETn,复位信号可以异步断言,但必须和时钟上升沿同步去断言。

复位期间对接口有如下要求:①主机接口必须驱动ARVALID,AWVALID,WVALID为低电平;②从机接口必须驱动RVALID,BVALID为低电平;③所有其他信号可以被驱动到任意值。

在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平。

3.2基本读写传输

握手过程

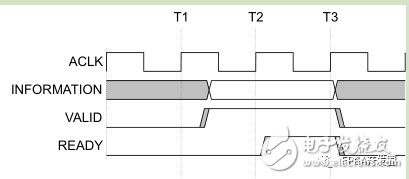

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。下图是几种握手机制:

图 3-1 VALID before READY 握手

图 3-2 READY before VALID 握手

图 3-3 VALID with READY 握手

通道信号要求

通道握手信号:每个通道有自己的xVALID/xREADY握手信号对。

写地址通道:当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言AWVALID,一个用来断言AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,知道时钟上升沿采样到从机的WREADY。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要断言WLAST信号。

写响应通道:从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)