一篇文章读懂读透FPGA AXI4 总线协议

机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言ARVALID,一个用来断言ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要断言RLAST。

通道间关系

-

AXI协议要求通道间满足如下关系:

-

写响应必须跟随最后一次burst的的写传输

-

读数据必须跟随数据对应的地址

通道握手信号的依耐关系

为防止死锁,通道握手信号需要遵循一定的依耐关系。①VALID信号不能依耐READY信号。②AXI接口可以等到检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY。下面有几个图表明依耐关系,单箭头指向的信号能在箭头起点信号之前或之后断言;双箭头指向的信号必须在箭头起点信号断言之后断言。

图 3-4 读传输握手依耐关系

图 3-5 写传输握手依耐关系

图 3-6 从机写响应握手依耐关系

3.3传输结构

地址结构

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

1)突发长度

ARLEN[7:0]决定读传输的突发长度,AWLEN[7:0]决定写传输的突发长度。AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1),AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

-

burst传输具有如下规则:

-

wraping burst ,burst长度必须是2,4,8,16

-

burst不能跨4KB边界

-

不支持提前终止burst传输

所有的组件都不能提前终止一次突发传输。然而,主机可以通过解断言所有的写的strobes来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。

注:对于FIFO,忽略后续读数据可能导致数据丢失,必须保证突发传输长度和要求的数据传输大小匹配。

突发大小

ARSIZE[2:0],读突发传输;AWSIZE[2:0],写突发传输。

AxSIZE[2:0] bytes in transfer

‘b000 1

‘b001 2

‘b010 4

‘b011 8

‘b100 16

‘b101 32

‘b110 64

‘b111 128

突发类型

FIXED:突发传输过程中地址固定,用于FIFO访问

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

AxBURST[1:0] burst type

‘b00 FIXED

‘b01 INCR

‘b10 WRAP

‘b11 Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

对于INCR突发和WRAP突发但没有到达回环边界,地址由下述方程决定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突发,突发边界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

数据读写结构

WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。

窄传输

当主机产生比它数据总线要窄的传输时,由地址和控制信号决定哪个字节被传输:

INCR和WRAP,不同的字节线决定每次burst传输的数据,FIXED,每次传输使用相同的字节线。

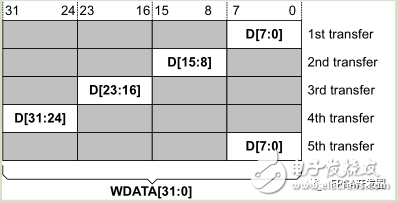

下图给出了5次突发传输,起始地址为0,每次传输为8bit,数据总线为32bit,突发类型为INCR。

图 3-7 窄传输示例1

下图给出3次突发,起始地址为4,每次传输32bit,数据总线为64bit。

图 3-8 窄传输示例2

非对齐传输

AXI支持非对齐传输。在大于一个字节的传输中,第一个自己的传输可能是非对齐的。如32-bit数据包起始地址在0x1002,非32bit对齐。

主机可以①使用低位地址线来表示非对齐的起始地

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)