set_operating_condition

跟的应该是db/lib里面定义的library name(eg.: tcbn28*************ccs),具体叫什么可以打开lib看第一行library后面跟的是什么,一般foundry提供的库也会是library_name.lib/library_name.db。你指定的哪个library就会用对应的db作为timing calculation的标准。

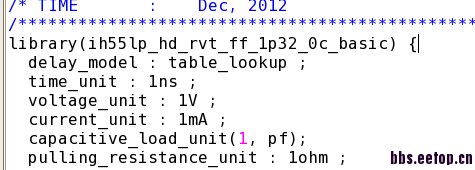

你好,我的lib里是这样的

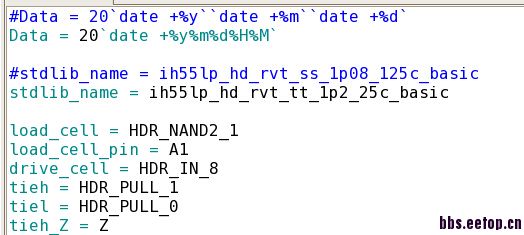

为什么写的是 $stdlib_name 呢? 不明白

肯定这之前某个地方有定义 set stdlib_name ih55lp_hd_rvt_ff_1p32_0c_basic

在哪个文件中?还是这个lib文件中吗?没看到啊

不是,应该是你其他的setup文件。你找找你之前source进去的文件里面或者前面的行里面哪个地方定义了这个变量。grep一下很容易找到的。

set search_path " ../db"

#set target_library "./lib/$stdlib_name.db"

#set link_library "* $target_library

source ./script/lib_link.path

source ./script/dont_use.tcl > ./report/$module.dont_use.log

#######################################################################

######## Read in design and library

########################################################################

set HDLCHDL-Compiler

catch {get_license $HDLC} result

while {$result ==0} {

sh sleep 10

catch {get_license $HDLC} result

}

#source ./script/read_ver.tcl

read_verilog ./code/$module.2.v

#read_verilog ../code/$module.v

current_design $module

link> ./report/$module.link.log

check_design > ./report/$module.check_design.log

set_operating_condition-library $stdlib_name

就这些了 另外grep怎么用呢

这个文件./script/lib_link.path里面找找看,grep的话到你的脚本目录下去抓关键字,看能不能找到那行。

set target_library {./db/ih55lp_hd_rvt_ss_1p08_125c_basic.db}

set link_library {./db/ih55lp_hd_rvt_ss_1p08_125c_basic.db}

#set target_library {./db/ih55lp_hd_rvt_tt_1p2_25c_basic.db}

#set link_library {./db/ih55lp_hd_rvt_tt_1p2_25c_basic.db}

#####verilog out#############

set write_name_nets_same_as_ports "true"

set verilogout_no_tri "true"

set verilogout_show_unconnected_pins "true"

set verilogout_higher_designs_first "true"

set bus_naming_style"%s_%d"

set bus_dimension_separator_style "_"

define_name_rules rule0 -restricted "\!\@\#\$\%\^\&\*\(\)\\\/\-\[\]\"\{\}" -case_insensitive -map {{{"%s[%d]","%s_%d"}}} -type net -target_bus_naming_style "%s_%d"

define_name_rules rule1 -restricted "\!\@\#\$\%\^\&\*\(\)\\\/\-\[\]\"\{\}" -case_insensitive -map {{{"%s[%d]","%s_%d"}}} -type cell

define_name_rules rule2 -restricted "\!\@\#\$\%\^\&\*\(\)\\\/\-\[\]\"\{\}" -case_insensitive -map {{{"%s[%d]","%s_%d"}}} -type port -target_bus_naming_style "%s_%d"

define_name_rules rule3 -remove_port_bus

define_name_rules rule4 -case_insensitive -map {{{"_reg[%d]","_reg_%d"}}} -type cell

也没有看到啊

在./script/dont_use.tcl文件中也有

set_dont_use $stdlib_name/HDR_AOI*

set_dont_use $stdlib_name/HDR_MAOI*

set_dont_use $stdlib_name/HDR_IAO*

set_dont_use $stdlib_name/HDR_IAO*

大侠 再继续问个问题 在 run.dc.tcl文件中还有这样一段话:

source ./sdc/$module.sdc > ./report/$module.sdc.logset_max_area 0

check_clocks > ./report/$module.unclocked.log

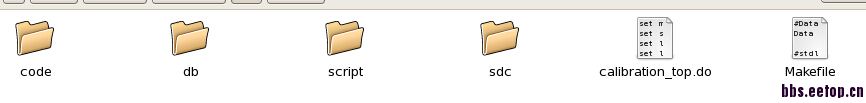

请问第一句什么意思 我的makefile中没有定义 module啊

makefile文件中唯一有module的就是

rm -rf report$@.do command.log

mkdir report

echo "set module $@" > $@.do

echo "set stdlib_name $(stdlib_name)" >> $@.do

echo "set load_cell $(load_cell)" >> $@.do

那run.dc.tcl文件中的module是什么意思呢 多谢啦,如果能顺带解释下 makefile文件中我贴出来的上面那段话就更感谢啦

Makefile 是用来产生*.do文件的。你贴出来的那段话就是定义变量的,module,stblib_name, load_cell都会定义,然后把这些命令写到*.do文件中。

两个问题啊第一,在11楼贴出的图中 没有定义 module这个变量,是不是少写啦,因为后面有用到 $module ,那这个module也该先定义 是吗

第二,.do文件是用来干什么的

多谢啦

echo "set module $@" > $@.do

这句就是定义module的。

综合要有综合的脚本,这个例子中综合的脚本是由Makefile来生成的*.do文件。

那按这么说 module是被定义成 $@了,然后把后面几句 echo 的内容写到了 module.do 文件中,但是我这里生成的是 calibration_top.do 文件啊

前面还有一句话其实 是这样的

syn=calibration_top

$(syn):

rm -rf report$@.do command.log

mkdir report

echo "set module $@" > $@.do

echo "set stdlib_name $(stdlib_name)" >> $@.do

echo "set load_cell $(load_cell)" >> $@.do

是不是就是因为 syn=calibration_top导致后面生成的是 calibration_top.do文件,而不是module.do文件呢

$(syn):

在Makefile里面表示目标,下面的是命令,表示完成这个目标需要做的事情。

在这个例子中: syn = calibration_top, $@就相当于是calibration_top的符号,所以

echo "set module $@" > $@.do的执行结果就是把 set module calibration_top 写到calibration_top.do的文件中。

恩 多谢啦!高手啊