sta signoff中set_operating_condition怎么加。

PT有三种分析模式,分别是single operation analysis mode,best case/worst case analysis,on-chip variation analysis。

1. single operation analysis模式

PT只使用一种operation condition的进行时序检查。

如只报告best-case的情况:

pt_shell>set_operation_conditions BEST

pt_shell>report_timing -delay_type min

如只报告worst-case的情况:

pt_shell>set_operation_conditions WORST

pt_shell>report_timing -delay_type max

2. best-case/worst-case analysis模式

PT使用best operation condition和worst operation condition的进行时序检查。在setup检查时,对所有路径使用max delay。在hold检查时,对所有路径使用min delay。

pt_shell>set_operation_conditions -min BEST -max WORST

pt_shell>report_timing -delay_type min

pt_shell>report_timing -delay_type max

3. on-chip variation模式

PT 进行保守时序分析。如在进行setup检查时,对发送寄存器clock路径和数据路径使用max delay,对锁存寄存器的clock路径使用min delay。在进行hold检查时,对发送寄存器clock路径和数据路径使用min delay,对锁存寄存器的clock路径使用max delay。

pt_shell>set_operation_conditions -analysis_type on_chip_variation -min MIN -max MAX

pt_shell>report_timing -delay_type min

pt_shell>report_timing -delay_type max

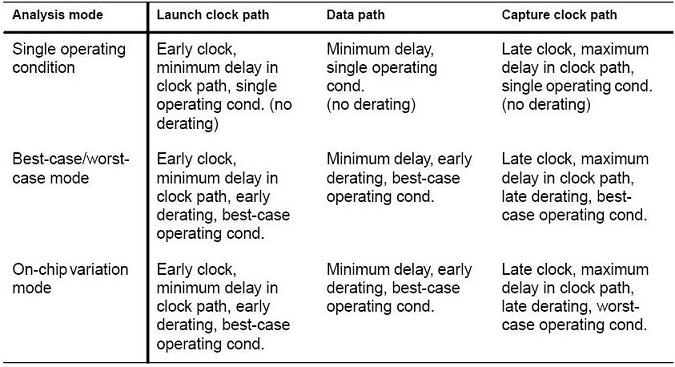

三种模式使用的参数对比表。

setup检查:

hold检查:

PT有三种分析模式,分别是single operation analysis mode,best case/worst case analysis,on-chip variation analysis。

1. single operation analysis模式

PT只使用一种operation condition的进行时序检查。

如只报告best-case的情况:

pt_shell>set_operation_conditions BEST

pt_shell>report_timing -delay_type min

如只报告worst-case的情况:

pt_shell>set_operation_conditions WORST

pt_shell>report_timing -delay_type max

2. best-case/worst-case analysis模式

PT使用best operation condition和worst operation condition的进行时序检查。在setup检查时,对所有路径使用max delay。在hold检查时,对所有路径使用min delay。

pt_shell>set_operation_conditions -min BEST -max WORST

pt_shell>report_timing -delay_type min

pt_shell>report_timing -delay_type max

3. on-chip variation模式

PT 进行保守时序分析。如在进行setup检查时,对发送寄存器clock路径和数据路径使用max delay,对锁存寄存器的clock路径使用min delay。在进行hold检查时,对发送寄存器clock路径和数据路径使用min delay,对锁存寄存器的clock路径使用max delay。

pt_shell>set_operation_conditions -analysis_type on_chip_variation -min MIN -max MAX

pt_shell>report_timing -delay_type min

pt_shell>report_timing -delay_type max

三种模式使用的参数对比表。

setup检查:

hold检查:

我是这么理解的:

每个库本身都是有operation_condition的,如果库打开里面有且只有一个operation_condition,report_lib 就可以看到。那pt就会默认用库中指定的这个operation_condition.

你是不需要做额外指定的,voltage也是, 每个domain 对应的lib自己也会考虑电压计算。

set_operation_condition的应用场景一般是:

1.库中包括多个condition,此时你可以用-max/-min来指定那个conditon作为max/min分析。

2.库中只有一个condition,但同时read了两个 不同condition下的库,此时你可以用-max_library/-min_library,指定哪个condition下的库做max/min分析

3.DMSA/MCMM 同时在一个sessition中分析不同corner,此时会load多个不同corner下的库,对每个senaro,就需要指定当前senaro用哪个库分析。

如果session中只是一个corner,且每个link lib 里面都只有一个operating condition ; 不管你设的是什么;各个cell都会用link lib中的那个operating condition;

还有就是是否存在一个.lib中定义了多个operating condition;如果定义多个,那么lib中timing are的look up table中的delay值如何适应这几个operating condition呢?

operation_condition是不能随便乱指定的,必须是lib中包含的,所以,当你的库本身就一个operation_condition,你其实指不指定都一样。

你的问题现在是针对不同的power domain 用一样的库,但voltage不一样对吧,voltage 是通过upf file指定的。如果你的design中用的同一种cell,比如buff,但工作在不同的domain voltage,你就必须指定两个不同的voltage lib 供pt计算。pt会找到对应的vol的库来计算delay(必须在load_upf,不然会报错,告诉你load了conflict的库),你只load其中一个vol corner下的库,计算的值是不准确的。 如果以你的例子,你就得load 0.95 V的lib 和1.05的lib。

在pt找不到对应vol的库的时候,他会找其他vol下的库,来推算你所需vol的库下的值。

report_timing -voltage

report_delay_calculation

你可以看到pt计算的细节。

对于一个库中有不同的operation_condition我是在书上看到的,具体的例子并没有遇到过,这种情况是有default_operation_condition的,不指定就用默认值。我觉得这个跟你现在碰到的问题可能不一样。

好吧,我也是自己看书加摸索的,可能有些地方也会有理解失误,仅供参考吧。

不同的voltage是通过用不同的.lib实现的,即高电压design用高电压的.lib,其他部分用普通lib(通过link_path_per_instance实现);并没有读upf;

另外我也是在S家的pdf中看到说一个.lib中可以有多个operating condition(这是另外一个问题);那么同一个look up table如何做到对不同operating condition做delay的转换呢。

我遇到的例子是:

1.同一个buff 用在1.05V 及 0.9V domain,同时load了1.05V lib及0.9V, 通过upf自动识别,并不需要定义set_operation_condition.

2.buffH用在 1.05,buffL 用在0.9V,不同的cell type, load LIBH_1.05V lib及 LIBL_0.9V两个lib,此时因为库不同也不用定义set_operation_condition.

恩,今天学习到了第三种方法link_path_per_instance~

刚才重读了一遍mannual

以下是pt 对voltage setting的相关定义:

PrimeTime derives cell instance voltages as follows:

oDefaultsupplyvoltagein library cell definition (voltage_map in

Liberty syntax)

o set_operating_conditions applied at the design level

o set_voltage on a supply net

o set_voltage on a PG pin

所以,感觉这个command本身是更多的是用在ocv条件下的max/min选择,因为它对voltage的指定是single rail的,对lvs等multi-rail的不适用。

至于第二个问题,因为没碰到过所以确实也不明白怎么实现的,我觉得应该每个operation_condition对应不同的查找表,或者,对应不同的derate参数之类的。

对于单个operation_condition的库。你要设定两个不同的voltage下的operation_condition,你势必要先load两个库,此时,不load_upf或set_link_path_per_instance,pt会报错,但一旦你用了这两个方法也没有必要再 set_operation_condition了,所以,我猜想这个command应该更多的是对应multi operation condition的库吧。恩,大概吧

恩 我也同意你的观点;

那你说 有多个operating condition 的lib它的delay怎么算的呢?look up table只有一个corner下的;

谢谢你的答复,你贴的图我也看过的,但是你好像没有理解为问题的意思;

其实在delay calculation 时在查找表之后还有一个step:

Fall Delay

。

scaling result for operating conditions

multiplying by 1 gives 1.62413

这是一个单一OC的库,所以scal的值为1,可以合理推断,对于multi-OC的库,会有不同的scale 参数。

这是我这边可以猜想到的合理解释了,没见过实物库确实很烦恼。

另外,在PT load sdf 的case,其实sdf是support multi-OC的,这些都是已经折现的delay值,此时也可以用这个set_operation_contion来指定OC。

恩 谢谢

scaling result for operating conditions

麻烦再问一下,这个你在哪看到的?我去看看

derate吧