DC综合求指导

时间:10-02

整理:3721RD

点击:

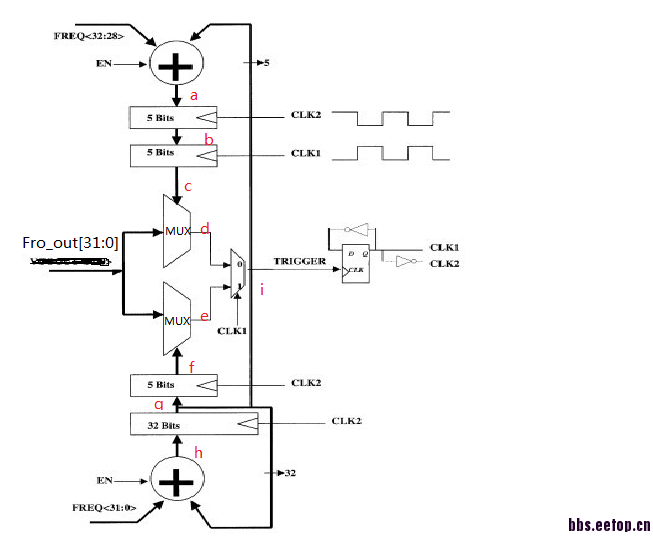

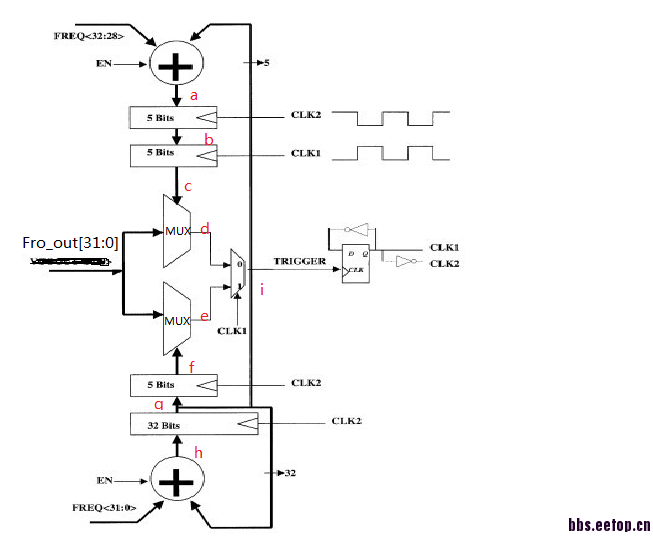

各位大侠好,我碰到一个多时钟端口的数字模块,结构如下:

它是一个数控振荡器,FREG[32:0]是数据控制位,它决定输出时钟clk1,clk2的频率大小。已经通过前仿真,说明功能是正确的。FROOUT0~FROOUT31是32个恒等相位差的时钟信号,频率都为100M,由于是32个时钟,所以FROOUT0~FROOUT31的相位差为10ns/32=312.5ps;32个时钟通过一个32选一MUX选择器,和2选1的选择器翻转后面的D触发器,也就是结构图中最右边的二分频。整个模块的输入端口是FROOUT0~FROOUT31,FREG[22:0];输出端口就只有clk1,clk2。像这种输出clk1,clk2又反馈回来触发中间的触发器,并且所有的MUX输出都是选择一路时钟信号的电路,该怎么去完善地约束它呢?请各位大侠指点一下。

它是一个数控振荡器,FREG[32:0]是数据控制位,它决定输出时钟clk1,clk2的频率大小。已经通过前仿真,说明功能是正确的。FROOUT0~FROOUT31是32个恒等相位差的时钟信号,频率都为100M,由于是32个时钟,所以FROOUT0~FROOUT31的相位差为10ns/32=312.5ps;32个时钟通过一个32选一MUX选择器,和2选1的选择器翻转后面的D触发器,也就是结构图中最右边的二分频。整个模块的输入端口是FROOUT0~FROOUT31,FREG[22:0];输出端口就只有clk1,clk2。像这种输出clk1,clk2又反馈回来触发中间的触发器,并且所有的MUX输出都是选择一路时钟信号的电路,该怎么去完善地约束它呢?请各位大侠指点一下。

这个模块单独约束做pr,做成硬core比较好。

单独的选择器d,e,i不适合动态时钟选择。

网上有正确的动态时钟选择电路。

在选择正确的动态时钟选择电路以后,约束就简单了。fro_out建立32个始终,相位可以一样,也可以是实际的,主要是限制时钟间的skew很小。clk2,clk1创建1个就够了。保证到选择器和触发器的延迟一至,看了下,为了便于约束时钟间skew,clk1和clk2还是设置2个始终,skew为半个周期约束。

选择器d,e,i的动态切换毛刺由动态选择时钟电路保证,时序上不能做到完全保证,因为时钟太多。

终于有大侠指导我了,还是这么详细地指导。多谢了 。虽然如此详细,但我还是个菜鸟,所以要慢慢消化大侠的指点。真心感谢!

请问大侠,你指的“动态时钟选择电路”哪儿有呢?我在百度里搜了一下好像没什么结果,能具体谈谈哪儿有参考电路嘛?