关于latch-up的一个小问题

时间:10-02

整理:3721RD

点击:

下午刚关于latc-up的英文资料,下面这一小段关于limited current latch-up的问题,这段英文看不太明白。

哪位大神帮忙具体解释下,不甚感激!

哪位大神帮忙具体解释下,不甚感激!

兄弟,这帖子发到电路设计中,回帖的应该多点!呵呵!

低调,低调。

同意2楼的建议

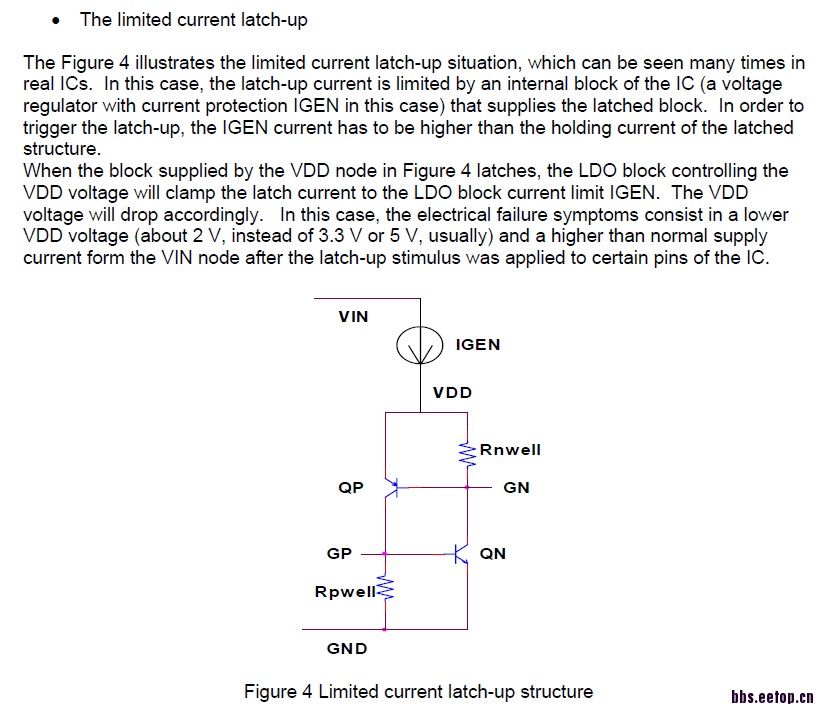

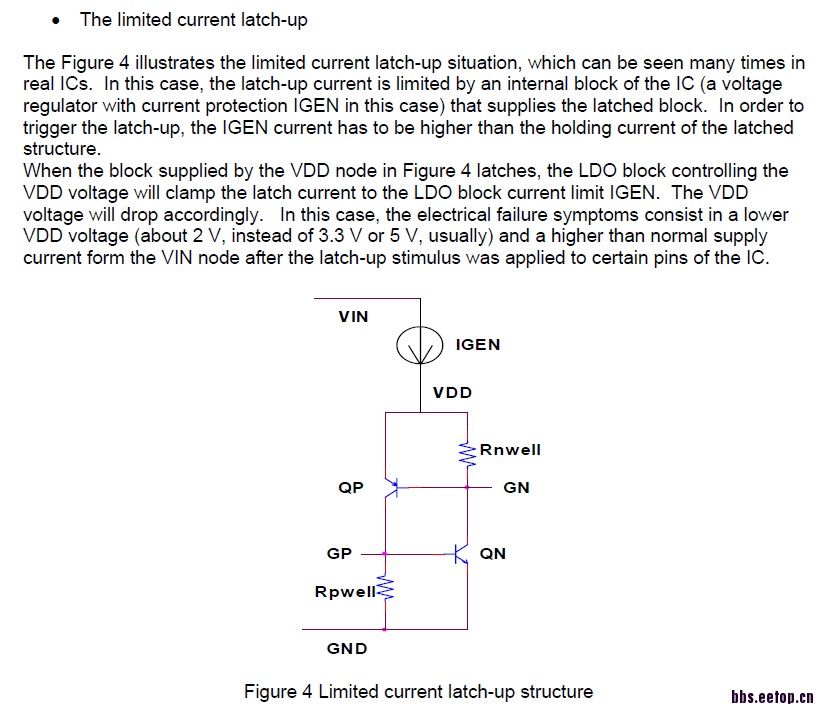

IGEN应该就是上面说的LDO,这个LDO的输出从图上看就是一个电压源,QP从图上看应该是一个PMOS,GN端应该就是QP的BODY,因为肼是能用来当电阻的,所以Rnwell的意义,其实就是QP这个PMOS的NTAP电位,当你的TAP电位离你的PMOS距离很远的话,Rnwell这个电阻就会变大,导致GN端的电压比QP的发射极要低,也就是你图上说的VDD是3.3V的话,如果Rnwell足够大,那么GN端的电压很有可能是2V,那么QP这个三极管,发射结反偏,集电结正偏,QP处于放大状态,然后这个结构就被LATCH了!小编了解了?

......呃。

这个不是解释为什么会发生latch,而是解释latch发生后,为什么会导致VDD降低导致function fail的问题。

thank you !

因为LDO能够提供的电流有限,这些电流全部从latch-up的结构流走,使得VDD被箝位到2v左右,导致内部function fail

学习学习