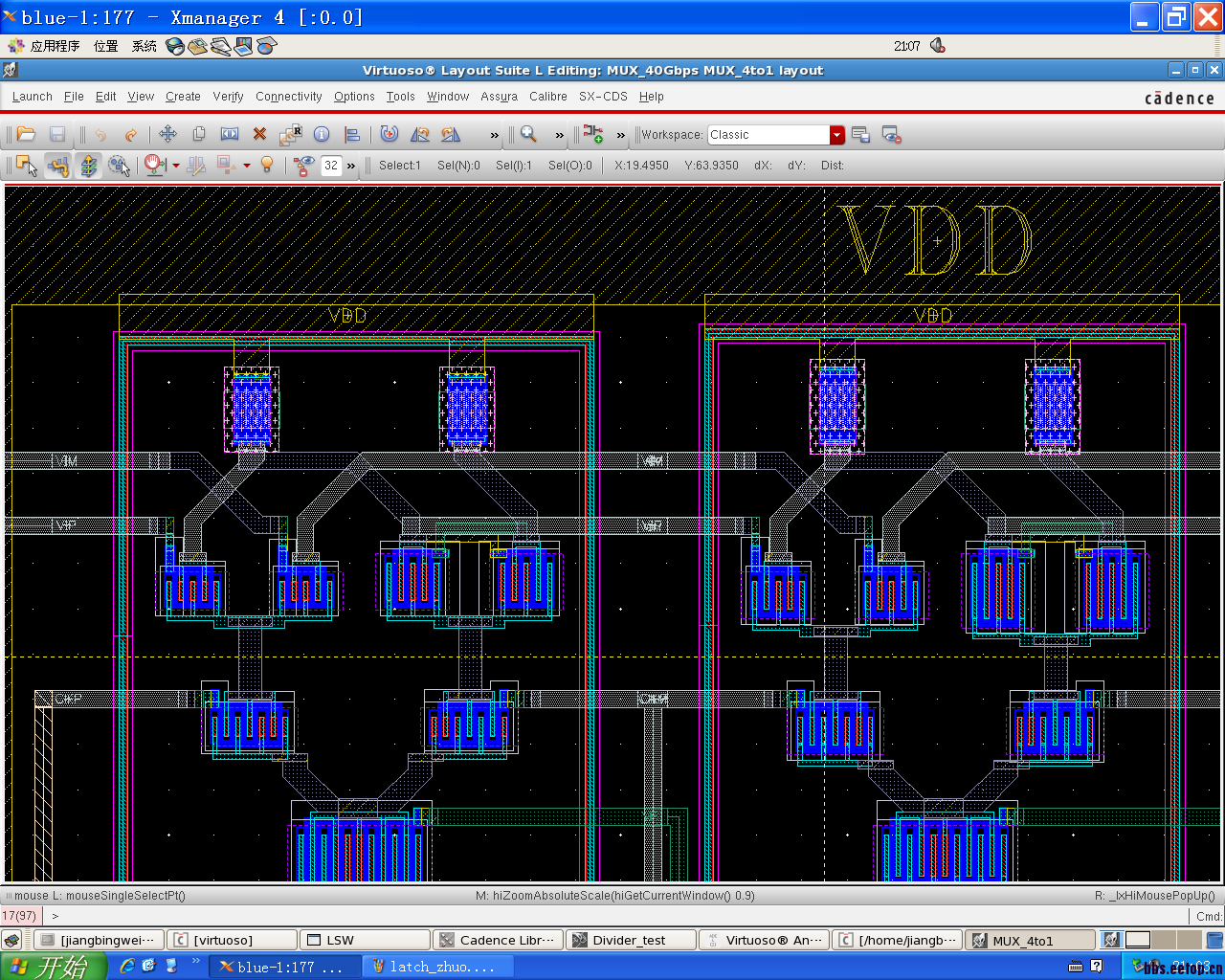

我画了几个CML的latch版图,请大家帮忙看下,哪个方案最好。

图呢?

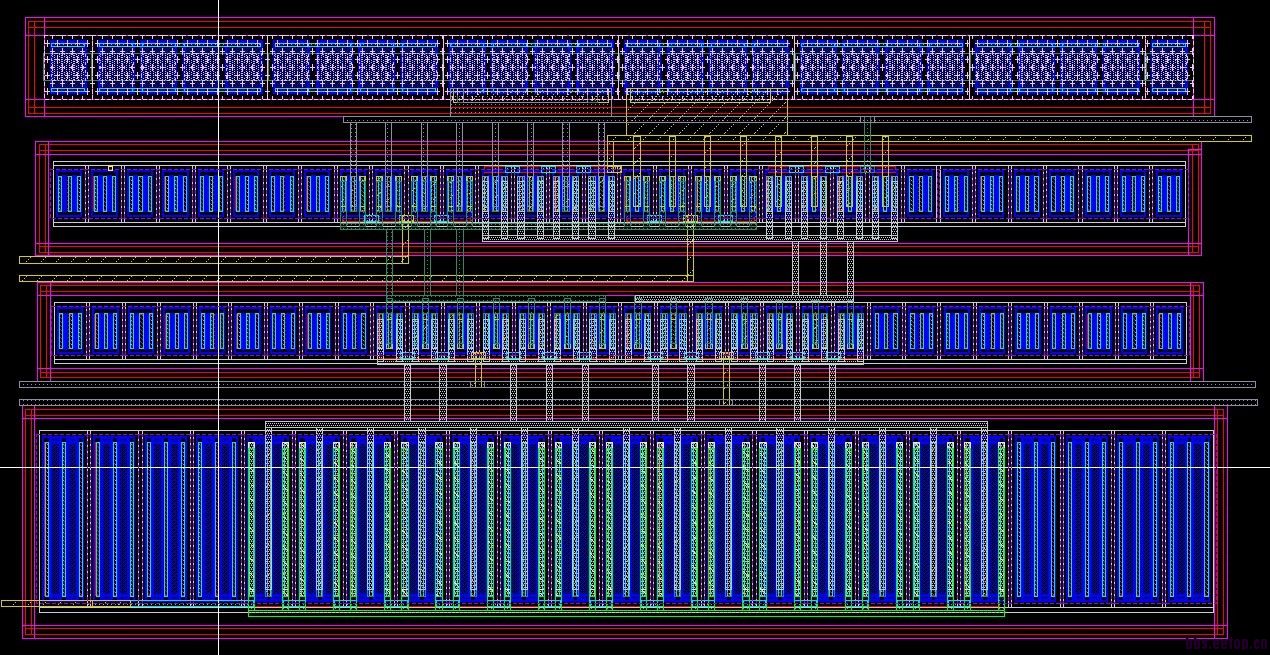

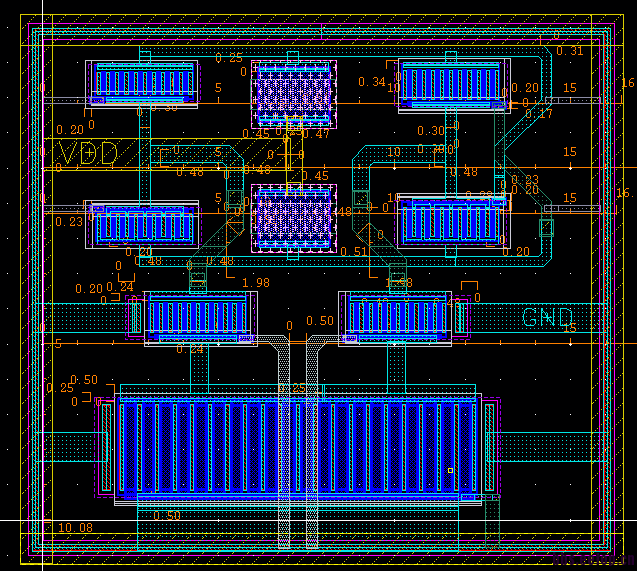

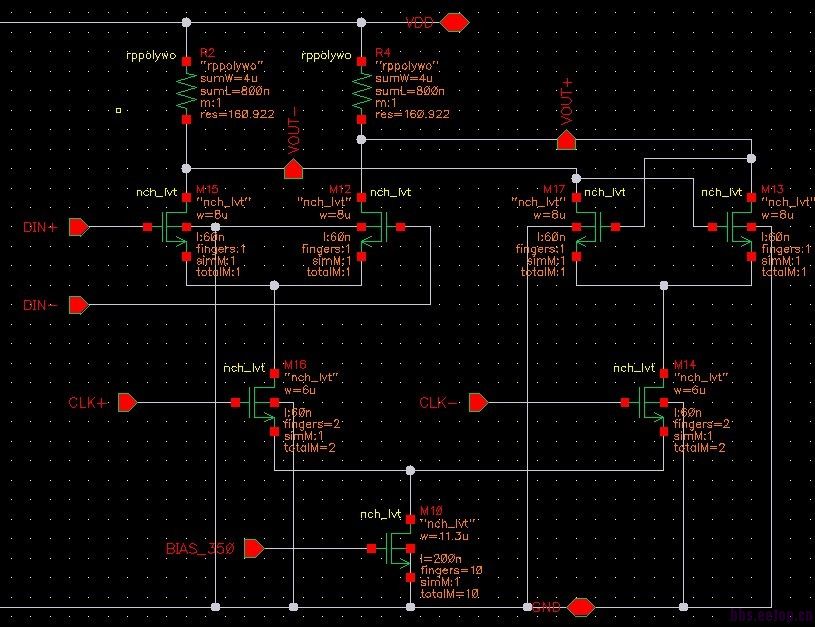

前三个是三个版本的版图,最后一个是电路图。请大家帮我看看。这个版图怎么画最好。我的data是25G,时钟是12.5GHz。

1和3相对比较费面积一点,其实我觉得2比较好点,你可以提取三个图的后仿参数仿真一下,看看寄生怎么样

其实都一般,我觉得把2再精简一下,能就紧凑尽量紧凑,size 小了,连线也短,寄生也小,其实layout 比circuit 跟靠个人天赋和感觉

为什么你觉得2比较好呢。2的输出有点不对称的。3的输出比较对称。而且2的面积可能比较大, dummy比较多。我是第一次画版图,请前辈指点了

这个latch本身不是一个对称的电路,真心不好画,请前辈指点啊

是不是因为频率太高,所以不能共源画?

请大牛帮我看看啊

2为什么要加那么多dummy

防止后防电流会不够,电路工作的速度上不去。到时候可以把dummy接到电路中。你觉得哪个好

首先,第三张图肯定是不行的,看起来好像对称,但是你把阻抗放到了中间,这样的话无疑增加了躁动,阻抗要远离静态模块,所以应该放在上面,各个功能块靠近配置,第二张图稍微好些,至于布线就看你的经验了,希望对你有帮助

个人也选第二张设计,如果要速度,寄生小的,面积小的,信号流流畅的一定快一点.

2好,我觉得高速里面,一个要注意信号的对称,另外一个就是想办法降低寄生,特别是cc

还有,你加那么多dummy,就不怕寄生多了?速度上不去要么是尾电流的原因,还有就是寄生太大,感觉你放这么多dummy反作用更大

继续个人意见,欢迎指教

我也感觉三画的比较对称。再把第三个画紧促点。

尾电流源管会不会线性啊,电流管尺寸这么大,时钟管尺寸这么小

2图,匹配较好,电阻和电路有隔离,噪声较小。

但是删掉多余dummy,留一个就够了,dummy是用来消除管子的边缘效应的,多了的dummy有害而无益。

电阻是万万不能放在电路内的,所以1和3都不可取。而且在可用面积足够的情况下,可以给电阻多包两圈guardring。

共源画是指什么意思啊?共质心么

电阻不能放在电路内啊?那要是电路有很多电阻怎么办。而且2怎么都画不了对称啊。我这个对时钟和数据要求严格对称啊。只有3可以做到,我现在用的是3,后防结果还可以。电阻的噪声在后仿真中能看的出来么

电阻独立放,用guardring隔离。就像2那样。噪声要做噪声分析仿真,你做后仿做了么?后仿提不出工艺偏差的。3图两个管子的距离较远,match肯定不如2。对匹配要求高的话,你所有的相同的管子都要做成插指结构和圆心对称的形式。

个人感觉2的寄生太大,3的走线寄生不match,高频的最好不要用那么多的metal1吧,个人感觉到上G的时候,寄生是最大的问题,而不是match

寄生是问题,可是我这个全是CML差分逻辑的电路,如果match的话,会有offset,几级级联起来offset会很大的,可能都达到上百mv了。

seeing

大哥什么意思啊