关于MOS管版图的问题,求指教!

时间:10-02

整理:3721RD

点击:

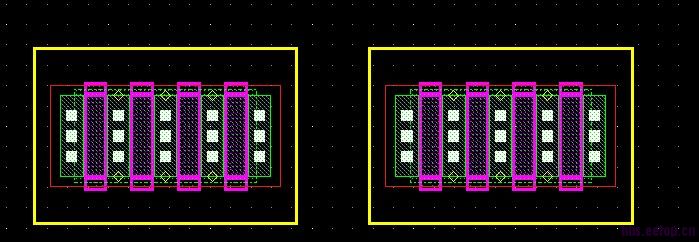

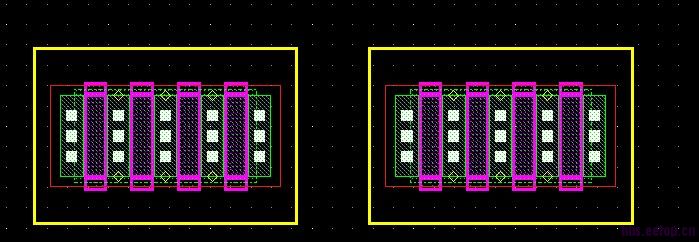

如下图所示的结构,连个PMOS源级都连接到VDD,在画版图时,有没有必要吧这两个mos管的源级重叠合并,具体见下图。或者说,什么时候需要合并,什么时候最好不要合并。谢谢指教!

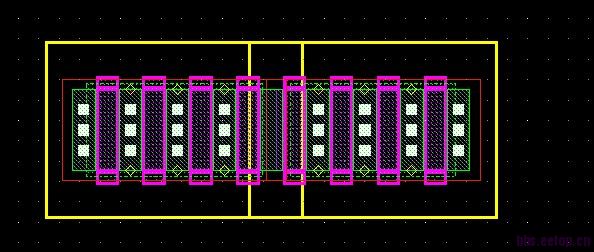

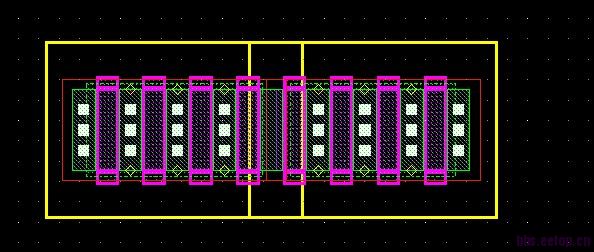

这个,16u一般来说还是有点大了。可以拆成8u或4u并联,用ABBA/BAAB方式匹配,然后可以把源合并。

单个管子,比如你就画成两个16u的管子,这样的话如果空间不是特别紧,最好不要合并。且采用源漏/源漏或漏源/漏源方式放置。

你指的重叠合并是指去掉接触孔吗?一般不这么做哦,数字部分为了省面积倒是常有。

还有就是如楼上所说,16u太大,分4个4u的做对称吧

谢谢! 其实这两个管子都是W/L=4/1的,只不过finger=4,所以显示成了16/1.

呵呵!谢谢。这些管子都是finger=4的4/1的管子。

哦 这样的话你要小心。

如果工艺比较先进 建议区分m和f,所以共用源或漏端要谨慎。

多小的工艺?不建议合并,40nm以下有二级效应

是0.5的BCD。

.18的时候这么搞过。没啥问题。40nm的时候有源间距会对阈值有影响

用两个(8/1)X2的吧,ABBA放置,感觉更好一些。

可以合并吧!但是没懂的是,这个图按通常的情况基本会要匹配,但如果原理图没有要求做匹配,就无所谓匹配与否吧?

0.5的工艺vibration不大吗?

差分放大最重要的就是差分对和有源负载了,而且搞不明白layout这边能随意拆MOS width吗?pre-simulation用的W16的spice model,拆成W4,M=4,寄生可能就变了,直接影响pre-simulation的结果,还是sansen书里写的好。

最好不要

一般拆管子都要和design商量的吧。其实大多数情况是design的标注写了拆成几个管子怎么match之类

对称嘛?