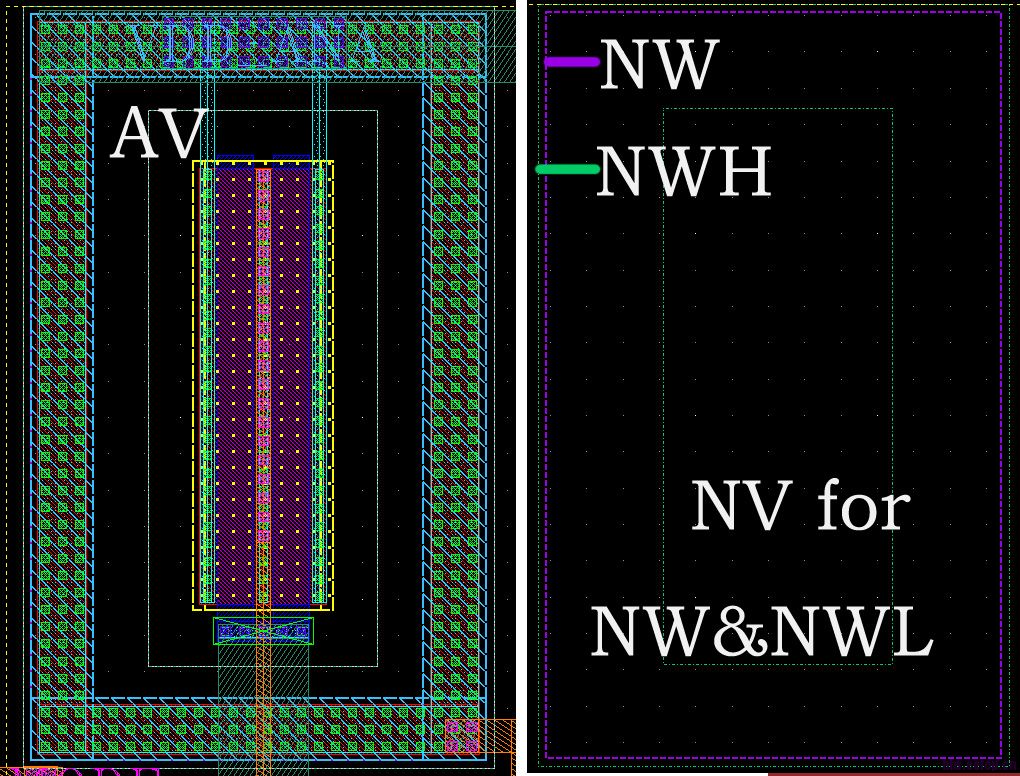

smic的工艺中NW(低压) 和 NWH(高压)

在版图中一个5V的P管上加了NWH的同时又加了NW,请问这会造成什么影响?

NWH是什么层?高压N阱?

如果是,那么一个普通的P管有必要加吗?当然,即使加了从功能上来说也不会错,只是要注意DRC了。

嗯,高压的N阱。DRC是过了,但芯片功能出问题了。

初步估计是这里的问题,现在是想找出原因,这么画了到底会影响些什么

你里边是高压管吧,那应该没问题.不过你确定HNW不是逻辑生成的吗?

模拟电路。自己画的。

高压NW会使结深增大 增加耐压能力里面又用低压的是不想让电气参数漂移,这样做应该不会影响功能。

但这样做会影响整体的参杂浓度,不会使NW和PSUB之间的PN结反向击穿的电压减小么?

感觉你上图标的有问题

一般高压nwell是一片的,nwell是一圈的作用只是给高压nwell电位接触的,你图上的只是貌似是将高压pmos坐在了nwell里面

这样这个高压pmos的耐压肯定不高

NWH 一般是logic operation得到的吧,用于3.3v等高压nw,和core power(1.8v)的普通NW相区别,

自己画的NWH 还没有见过,

高压阱(deep nwell)是可以这样画的。

有些工艺里面deepnwell 是一片,nwell是一圈,是因为deep nwell是作为了一个掩埋层,外围的nwell是电位接触和隔离的作用;

但是在有些工艺里面,是有单独的deep nwell(真实的一层mask)去用作高压器件的,里面没有用nwell环做电位接触。

有时可以把低压的nmos坐在高压阱里面,为了隔离噪声或者是其他的目的。

但是为啥lz的图片里面高压阱和低压阱都用了呢?

电路性能方面等待其他高手确认。

http://www.edaboard.com/thread247928.html

个人觉得画上NWH应该对Pmos有好处