关于电容LVS的问题求助

时间:10-02

整理:3721RD

点击:

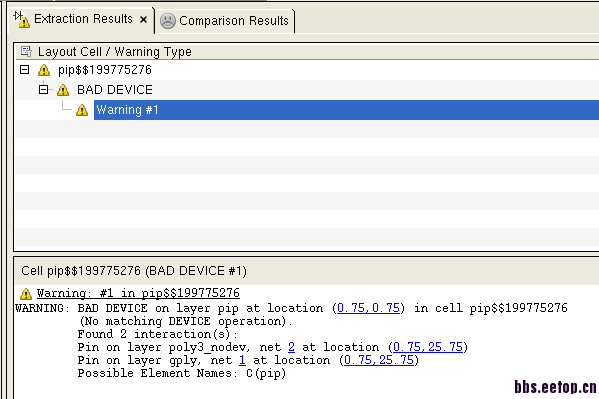

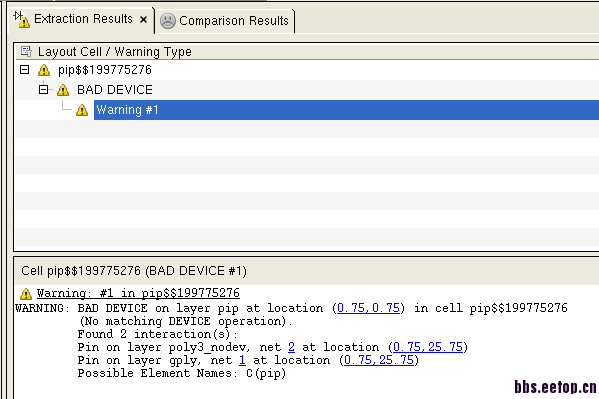

在做LVS的时候,pip电容版图提取不了,这是为什么呢?单独只画一个电容,做lvs,会显示说nothing in layout。

lvs report如下OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Properties missing on instances in source.

Error:Components with non-identical signal pins.

Error:Different numbers of instances.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

INCORRECTCHAOSGEN_LAYOUT1CHAOSGEN_LAYOUT1

**************************************************************************************************************

LVS PARAMETERS

**************************************************************************************************************

o LVS Setup:

LVS COMPONENT TYPE PROPERTYelement

LVS COMPONENT SUBTYPE PROPERTYmodel

LVS PIN NAME PROPERTYphy_pin

LVS POWER NAME"VCC" "vcc" "vcc!" "VDD" "vdd" "vdd!" "DVDD"

LVS GROUND NAME"GND" "gnd" "gnd!" "VSS" "vss" "vss!" "DVSS"

LVS CELL SUPPLYNO

LVS RECOGNIZE GATESALL

LVS IGNORE PORTSNO

LVS CHECK PORT NAMESNO

LVS IGNORE TRIVIAL NAMED PORTSNO

LVS BUILTIN DEVICE PIN SWAPYES

LVS ALL CAPACITOR PINS SWAPPABLEYES

LVS DISCARD PINS BY DEVICENO

LVS SOFT SUBSTRATE PINSNO

LVS INJECT LOGICYES

LVS EXPAND UNBALANCED CELLSYES

LVS FLATTEN INSIDE CELLNO

LVS EXPAND SEED PROMOTIONSNO

LVS PRESERVE PARAMETERIZED CELLSNO

LVS GLOBALS ARE PORTSYES

LVS REVERSE WLNO

LVS SPICE PREFER PINSNO

LVS SPICE SLASH IS SPACEYES

LVS SPICE ALLOW FLOATING PINSYES

// LVS SPICE ALLOW INLINE PARAMETERS

LVS SPICE ALLOW UNQUOTED STRINGSNO

LVS SPICE CONDITIONAL LDDNO

LVS SPICE CULL PRIMITIVE SUBCIRCUITSNO

LVS SPICE IMPLIED MOS AREANO

// LVS SPICE MULTIPLIER NAME

LVS SPICE OVERRIDE GLOBALSNO

LVS SPICE REDEFINE PARAMNO

LVS SPICE REPLICATE DEVICESNO

LVS SPICE SCALE X PARAMETERSNO

LVS SPICE STRICT WLNO

// LVS SPICE OPTION

LVS STRICT SUBTYPESNO

LVS EXACT SUBTYPESNO

LAYOUT CASENO

SOURCE CASENO

LVS COMPARE CASENO

LVS DOWNCASE DEVICENO

LVS REPORT MAXIMUM50

LVS PROPERTY RESOLUTION MAXIMUM200

// LVS SIGNATURE MAXIMUM

LVS FILTER UNUSED OPTIONRC LAYOUT

// LVS REPORT OPTION

LVS REPORT UNITSYES

// LVS NON USER NAME PORT

// LVS NON USER NAME NET

// LVS NON USER NAME INSTANCE

// Reduction

LVS REDUCE SERIES MOSNO

LVS REDUCE PARALLEL MOSYES

LVS REDUCE SEMI SERIES MOSNO

LVS REDUCE SPLIT GATESYES

LVS REDUCE PARALLEL BIPOLARNO

LVS REDUCE SERIES CAPACITORSNO

LVS REDUCE PARALLEL CAPACITORSYES

LVS REDUCE SERIES RESISTORSYES

LVS REDUCE PARALLEL RESISTORSYES

LVS REDUCE PARALLEL DIODESNO

LVS REDUCEC(pip)PARALLEL [ TOLERANCE c_length 0 c_width 0 ]

LVS REDUCEMNPARALLEL [ TOLERANCE l 1 ]

LVS REDUCEMPPARALLEL [ TOLERANCE l 1 ]

LVS REDUCTION PRIORITYPARALLEL

LVS SHORT EQUIVALENT NODESNO

// Trace Property

TRACE PROPERTYrr r 1

TRACE PROPERTYmnw w 1

TRACE PROPERTYmnl l 1

TRACE PROPERTYmpw w 1

TRACE PROPERTYmpl l 1

TRACE PROPERTYd(pn_5p0)a a 1

TRACE PROPERTYd(pn_3p3)a a 1

TRACE PROPERTYd(np_5p0)a a 1

TRACE PROPERTYd(np_3p3)a a 1

TRACE PROPERTYd(nwp)a a 1

TRACE PROPERTYd(dnwp)a a 1

TRACE PROPERTYd(np_5p0_esd)a a 1

TRACE PROPERTYd(np_3p3_esd)a a 1

TRACE PROPERTYc(pip)c_length c_length 1

TRACE PROPERTYc(pip)c_width c_width 1

TRACE PROPERTYc(pip)m m 1

**************************************************************************************************************

COMPONENT TYPES WITH NON-IDENTICAL SIGNAL PINS

**************************************************************************************************************

(Cells with the same ( or corresponding ) name that have different signal

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:R (3 pins): (p n) sub

Layout Extra Pins:sub

Source Component Type:R (2 pins): (p n)

No Extra Pins.

CELL COMPARISON RESULTS ( TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Properties missing on instances in source.

Error:Different numbers of instances (see below).

LAYOUT CELL NAME:CHAOSGEN_LAYOUT1

SOURCE CELL NAME:CHAOSGEN_LAYOUT1

--------------------------------------------------------------------------------------------------------------

INITIAL NUMBERS OF OBJECTS

--------------------------

LayoutSourceComponent Type

--------------------------

Ports:44

Nets:3838

Instances:6331*MN (4 pins)

4423*MP (4 pins)

01*C (2 pins)

44R (2 pins)

------------

Total Inst:11159

NUMBERS OF OBJECTS AFTER TRANSFORMATION

---------------------------------------

LayoutSourceComponent Type

--------------------------

Ports:44

Nets:2727

Instances:2121MN (4 pins)

1313MP (4 pins)

01*C (2 pins)

11R (2 pins)

22_nor2v (5 pins)

11_smn2b (5 pins)

22_smn2v (4 pins)

33_sup2v (4 pins)

------------

Total Inst:4344

* = Number of objects in layout different from number in source.

**************************************************************************************************************

INCORRECT OBJECTS

**************************************************************************************************************

LEGEND:

-------

ne= Naming Error (same layout name found in source

circuit, but object was matched otherwise).

**************************************************************************************************************

SOURCE ERRORS

DISC#

**************************************************************************************************************

Properties Missing on Instances:

1propertyc_widthnot found onCC0 (C)

2propertyc_lengthnot found onCC0 (C)

**************************************************************************************************************

INCORRECT INSTANCES

DISC#LAYOUT NAMESOURCE NAME

**************************************************************************************************************

3** missing instance **CC0C(PIP)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:4400

Nets:272700

Instances:212100MN(NMOS_3P3)

131300MP(PMOS_3P3)

0001C(PIP)

1100R(NPLUS_U)

2200_nor2v

1100_smn2b

2200_smn2v

3300_sup2v

--------------------------------

Total Inst:434301

o Statistics:

2 source properties were missing.

79 layout mos transistors were reduced to 26.

53 mos transistors were deleted by parallel reduction.

4 series layout resistors were reduced to 1.3 connecting nets were deleted.

4 series source resistors were reduced to 1.3 connecting nets were deleted.

o Initial Correspondence Points:

Ports:VDD VSS CHAOS_BIN CLK

**************************************************************************************************************

SUMMARY

**************************************************************************************************************

Total CPU Time:0 sec

Total Elapsed Time:0 sec

lvs report如下OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Properties missing on instances in source.

Error:Components with non-identical signal pins.

Error:Different numbers of instances.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

INCORRECTCHAOSGEN_LAYOUT1CHAOSGEN_LAYOUT1

**************************************************************************************************************

LVS PARAMETERS

**************************************************************************************************************

o LVS Setup:

LVS COMPONENT TYPE PROPERTYelement

LVS COMPONENT SUBTYPE PROPERTYmodel

LVS PIN NAME PROPERTYphy_pin

LVS POWER NAME"VCC" "vcc" "vcc!" "VDD" "vdd" "vdd!" "DVDD"

LVS GROUND NAME"GND" "gnd" "gnd!" "VSS" "vss" "vss!" "DVSS"

LVS CELL SUPPLYNO

LVS RECOGNIZE GATESALL

LVS IGNORE PORTSNO

LVS CHECK PORT NAMESNO

LVS IGNORE TRIVIAL NAMED PORTSNO

LVS BUILTIN DEVICE PIN SWAPYES

LVS ALL CAPACITOR PINS SWAPPABLEYES

LVS DISCARD PINS BY DEVICENO

LVS SOFT SUBSTRATE PINSNO

LVS INJECT LOGICYES

LVS EXPAND UNBALANCED CELLSYES

LVS FLATTEN INSIDE CELLNO

LVS EXPAND SEED PROMOTIONSNO

LVS PRESERVE PARAMETERIZED CELLSNO

LVS GLOBALS ARE PORTSYES

LVS REVERSE WLNO

LVS SPICE PREFER PINSNO

LVS SPICE SLASH IS SPACEYES

LVS SPICE ALLOW FLOATING PINSYES

// LVS SPICE ALLOW INLINE PARAMETERS

LVS SPICE ALLOW UNQUOTED STRINGSNO

LVS SPICE CONDITIONAL LDDNO

LVS SPICE CULL PRIMITIVE SUBCIRCUITSNO

LVS SPICE IMPLIED MOS AREANO

// LVS SPICE MULTIPLIER NAME

LVS SPICE OVERRIDE GLOBALSNO

LVS SPICE REDEFINE PARAMNO

LVS SPICE REPLICATE DEVICESNO

LVS SPICE SCALE X PARAMETERSNO

LVS SPICE STRICT WLNO

// LVS SPICE OPTION

LVS STRICT SUBTYPESNO

LVS EXACT SUBTYPESNO

LAYOUT CASENO

SOURCE CASENO

LVS COMPARE CASENO

LVS DOWNCASE DEVICENO

LVS REPORT MAXIMUM50

LVS PROPERTY RESOLUTION MAXIMUM200

// LVS SIGNATURE MAXIMUM

LVS FILTER UNUSED OPTIONRC LAYOUT

// LVS REPORT OPTION

LVS REPORT UNITSYES

// LVS NON USER NAME PORT

// LVS NON USER NAME NET

// LVS NON USER NAME INSTANCE

// Reduction

LVS REDUCE SERIES MOSNO

LVS REDUCE PARALLEL MOSYES

LVS REDUCE SEMI SERIES MOSNO

LVS REDUCE SPLIT GATESYES

LVS REDUCE PARALLEL BIPOLARNO

LVS REDUCE SERIES CAPACITORSNO

LVS REDUCE PARALLEL CAPACITORSYES

LVS REDUCE SERIES RESISTORSYES

LVS REDUCE PARALLEL RESISTORSYES

LVS REDUCE PARALLEL DIODESNO

LVS REDUCEC(pip)PARALLEL [ TOLERANCE c_length 0 c_width 0 ]

LVS REDUCEMNPARALLEL [ TOLERANCE l 1 ]

LVS REDUCEMPPARALLEL [ TOLERANCE l 1 ]

LVS REDUCTION PRIORITYPARALLEL

LVS SHORT EQUIVALENT NODESNO

// Trace Property

TRACE PROPERTYrr r 1

TRACE PROPERTYmnw w 1

TRACE PROPERTYmnl l 1

TRACE PROPERTYmpw w 1

TRACE PROPERTYmpl l 1

TRACE PROPERTYd(pn_5p0)a a 1

TRACE PROPERTYd(pn_3p3)a a 1

TRACE PROPERTYd(np_5p0)a a 1

TRACE PROPERTYd(np_3p3)a a 1

TRACE PROPERTYd(nwp)a a 1

TRACE PROPERTYd(dnwp)a a 1

TRACE PROPERTYd(np_5p0_esd)a a 1

TRACE PROPERTYd(np_3p3_esd)a a 1

TRACE PROPERTYc(pip)c_length c_length 1

TRACE PROPERTYc(pip)c_width c_width 1

TRACE PROPERTYc(pip)m m 1

**************************************************************************************************************

COMPONENT TYPES WITH NON-IDENTICAL SIGNAL PINS

**************************************************************************************************************

(Cells with the same ( or corresponding ) name that have different signal

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:R (3 pins): (p n) sub

Layout Extra Pins:sub

Source Component Type:R (2 pins): (p n)

No Extra Pins.

CELL COMPARISON RESULTS ( TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Properties missing on instances in source.

Error:Different numbers of instances (see below).

LAYOUT CELL NAME:CHAOSGEN_LAYOUT1

SOURCE CELL NAME:CHAOSGEN_LAYOUT1

--------------------------------------------------------------------------------------------------------------

INITIAL NUMBERS OF OBJECTS

--------------------------

LayoutSourceComponent Type

--------------------------

Ports:44

Nets:3838

Instances:6331*MN (4 pins)

4423*MP (4 pins)

01*C (2 pins)

44R (2 pins)

------------

Total Inst:11159

NUMBERS OF OBJECTS AFTER TRANSFORMATION

---------------------------------------

LayoutSourceComponent Type

--------------------------

Ports:44

Nets:2727

Instances:2121MN (4 pins)

1313MP (4 pins)

01*C (2 pins)

11R (2 pins)

22_nor2v (5 pins)

11_smn2b (5 pins)

22_smn2v (4 pins)

33_sup2v (4 pins)

------------

Total Inst:4344

* = Number of objects in layout different from number in source.

**************************************************************************************************************

INCORRECT OBJECTS

**************************************************************************************************************

LEGEND:

-------

ne= Naming Error (same layout name found in source

circuit, but object was matched otherwise).

**************************************************************************************************************

SOURCE ERRORS

DISC#

**************************************************************************************************************

Properties Missing on Instances:

1propertyc_widthnot found onCC0 (C)

2propertyc_lengthnot found onCC0 (C)

**************************************************************************************************************

INCORRECT INSTANCES

DISC#LAYOUT NAMESOURCE NAME

**************************************************************************************************************

3** missing instance **CC0C(PIP)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:4400

Nets:272700

Instances:212100MN(NMOS_3P3)

131300MP(PMOS_3P3)

0001C(PIP)

1100R(NPLUS_U)

2200_nor2v

1100_smn2b

2200_smn2v

3300_sup2v

--------------------------------

Total Inst:434301

o Statistics:

2 source properties were missing.

79 layout mos transistors were reduced to 26.

53 mos transistors were deleted by parallel reduction.

4 series layout resistors were reduced to 1.3 connecting nets were deleted.

4 series source resistors were reduced to 1.3 connecting nets were deleted.

o Initial Correspondence Points:

Ports:VDD VSS CHAOS_BIN CLK

**************************************************************************************************************

SUMMARY

**************************************************************************************************************

Total CPU Time:0 sec

Total Elapsed Time:0 sec

1. Please check cap type for layout and design (3 pins and 2 pins are different).

2. Please check lvs rule deck check cap by value or w/l.

請CHK你PIP CAP的path是否要蓋某層symbol才能被識別;

請CHK你runlvs的path是否正確;

請CHK你log.com的spi是否相符;

還要看看是否有多蓋不應該蓋的層.