请教PLL锁定问题

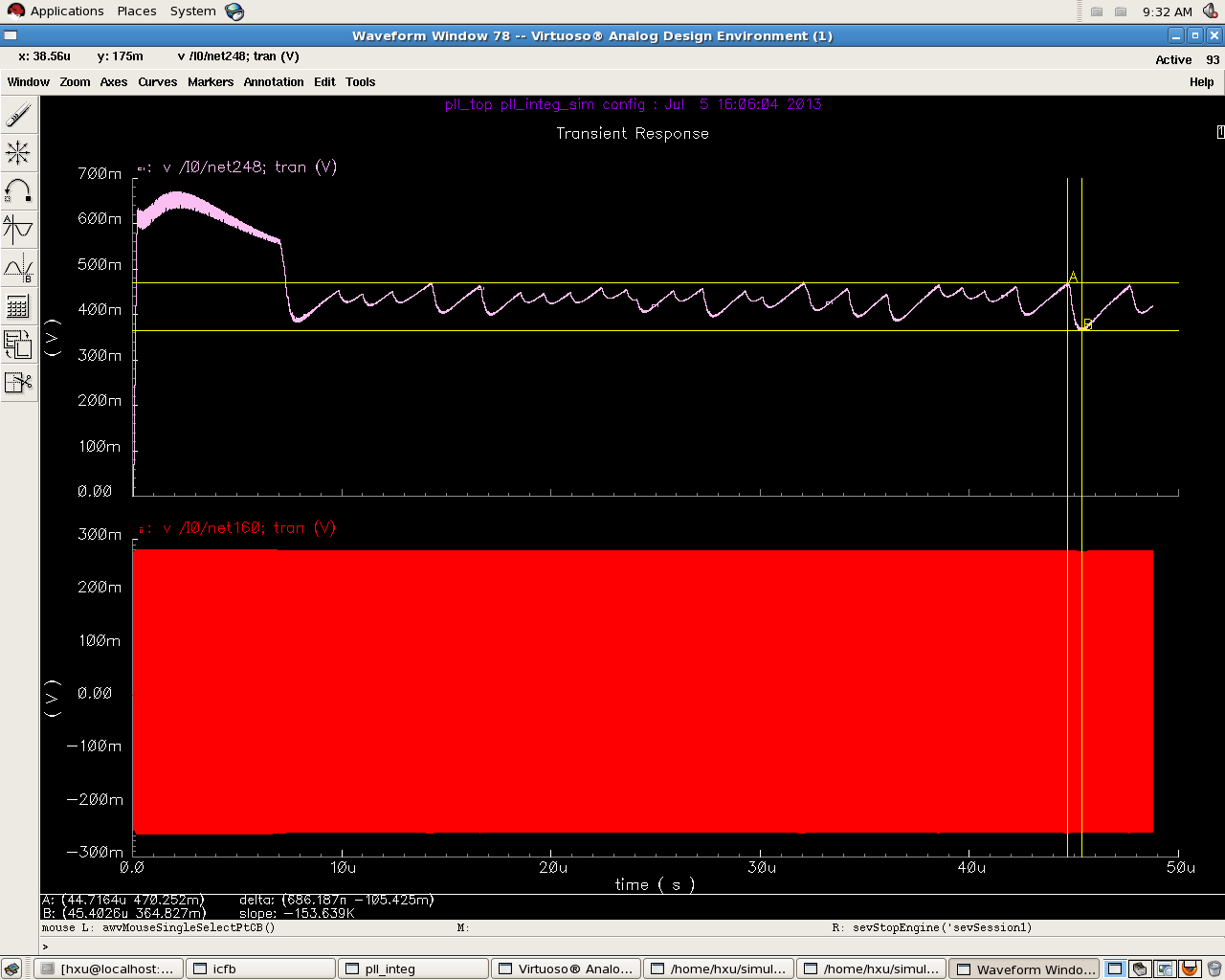

现在osc,vco均用理想模型,理论上vtune=500mV的时候锁定。但是vtune曲线会一直在400mV附近以100mV左右的幅度不规则摆动。感觉也不像是震荡。见上图。

另外,如果将divider去掉,用16M的vco输出直接给pfd(osc=16M),仅有pfd、cp是实际电路,仿真是能锁定的,能说明pfdcp没有问题吗?见下图。

有谁知道是怎么回事吗?谢谢!

[upload=1][/upload][upload=2][/upload]

※ FROM: 159.226.228]

※ 来源:·水木社区 http://www.newsmth.net·[FROM: 159.226.228]

divider换成理想的试试。可能是divider跑不了3.2G,出来的feedback clock错了

divider是不是有个dc阈值,把那个改成0就好

你已经debug得很清楚了啊~divider换成理想的就行,那当然就是divider的问题了~鉴于VC

电压一直小于标称的500mV,说明divider的实际分配比偏低,大概率就是divider高频分不

对,单仿divider试试吧~

电路中有一个/2分频,与一个/100的吞脉冲整数分频,将/2分频换成理想的,还是不能锁定。我再将/100分频换成理想的试试

divider单独仿过,一个输入信号周期,对应200个输出信号周期,仅仅通过这种方法确定分频比正确。而且在环路中,数周期也是对的。不知道还要如何验证divider的分频比呢?

你先用理想divider试一下,如果没错应该是divider的问题

或者是vco的过零和divider的过零不匹配

vco gain 多大?

看图好像16MHz Vtune也是500mV, 难道不应该低一些 ?

请问vco的过零与divider的过零不匹配是指的什么呢?新手设计pll,多多包涵。

vco理想的,不同的频率设的gain不一样,都使得在500mv的时候能够振在3.2GHz或者16MHz。

那就不能确定是不是vco没有问题,有可能是gain不一样造成pll 的loop不stable吧。

至于divider,你可以先试试divider=2,32M 能不能稳(就用16M的那个vco),然后试试4,8,32,64,直到200,看看什么时候出现问题。

用config仿divider,在端口设置中,如果设置input的a2d_tx为1ns,那么分频比数周期是正确的,但如果设置a2d_tx为1ps,那么分频比明显要小多了。不是精度越高应该越准确吗?

到最后摆幅差不多几十到一百mv,看起来不像是stable的问题。

下面我再根据你的建议仿一下divider。

可能出现在a2d的问题上

你可以看看inp inn交点是不是你那个比较器输出边沿

我曾经写过一个vams的divider,用了一个0.5V的阈值而不是0V的阈值,出来的结果

很你的很类似