仿真PFD延时时锁相环不锁定的问题

时间:12-12

整理:3721RD

点击:

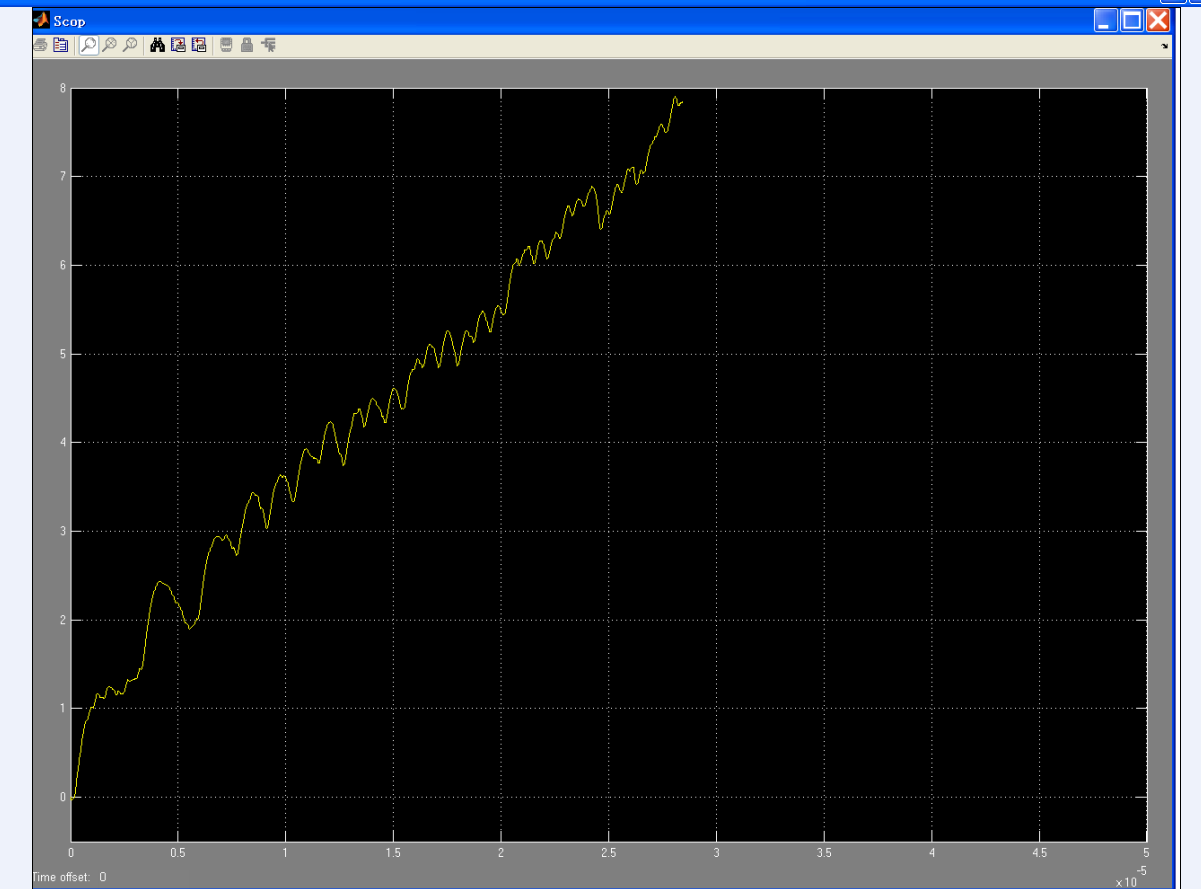

在用simulink仿真PLL是否锁定时,采用offset PFD时(图1),vco的控制电压如图2,显

示不锁定。但是采用overlapping PFD(如图3)时就可以锁定,Fref=50M,延时都为3Ns。

请教为何图1 的电路会不锁定,并且在cadence中仿真图一电路的鉴相曲线时Age(up-

down)在1.8v左右摆动,而不是理想的斜线,大家以前是否也遇到过这种问题!

示不锁定。但是采用overlapping PFD(如图3)时就可以锁定,Fref=50M,延时都为3Ns。

请教为何图1 的电路会不锁定,并且在cadence中仿真图一电路的鉴相曲线时Age(up-

down)在1.8v左右摆动,而不是理想的斜线,大家以前是否也遇到过这种问题!

kvco设定为30M/V 现在调整为10-100M/V 共分十次调节 但是还是没有锁定 是不是这种

offset 的PFD我设计的有问题?图4是simulink的PFD模型 中间的memory是为了消除代数环

而加的

你可以试试把vco模型化到一个比例,一个积分,调大增益,让vco输出是一条笔直的斜线。