一个关于运放的问题

请大家给予指教,谢谢!

开环运放的输出是高阻抗点,必须通过反馈才能定住它的直流电平,可以接成单位反馈的形式,用stb 分析其环路增益,即开环增益。

不理解,你又不是全差分,怕工作点没有? 只要你的偏置没有限制headroom,怕什么静态工作点,EA运放闭环使用时,输出点电平不劳您操心,它自己会找到合适的工作点。

你现在看到所谓的输出摆幅受限,可能还是沟道调制效应导致的系统失调(M7&M8 M5&M6),因为没有闭环,所以就被你理解成输出摆幅不够了。

首先谢谢你的回复。

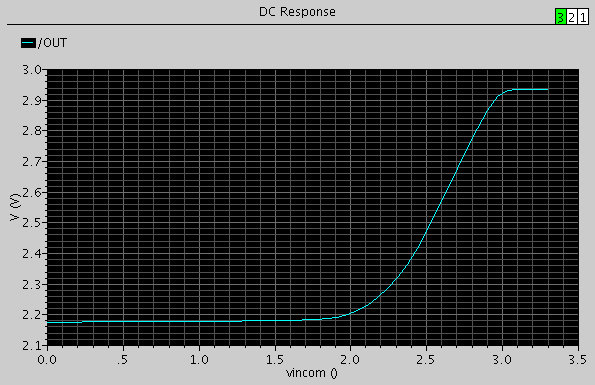

您说的方式是可以,但是我通过DC扫描发现不管我的输入共模电平是多少,输出电平始终大于2V,这样的话就没法使我的输出静态工作电平调到VDD/2,按照现在仿真的结果来看输出的摆幅受限。我想问的就是造成这样的原因是什么,或者调整哪个参数可以达到我想要的那种效果。不知道您有遇到过这种问题没?

您好。您说得很有道理,我不是担心它找不到合适的工作点。我的思路是这样的:我想先通过DC仿真找到斜率最大的点来确定AC分析的输入工作点。这个工作点应该使输出电平在VDD/2左右,以便达到最大的摆幅。但是现在输出点始终处于较高电平,我调了好几个参数都降不下去。在以前的设计中还没遇到过这种情况。

我也尝试一下闭环仿真吧,看看到底什么问题。

总之感觉这个仿真结果肯定不大对,就是不知道再该往哪个方向调整参数了。

谢谢!

双变单部分的固有失调引起的吧,加差分电压调整到VDD/2好了

您说是双变单的固有失调电压引起的?这个我还真的不是很清楚,以为在仿真的时候就没问题了。那这种情况下要做AC仿真该如何定工作点呢?

找到原因了,感谢各位同行给予的指点和提醒。

输出支路上下电流不匹配吧

你调到VDD/2后的增益要比现在大很多么?

输出支路上下电流肯定是一样的,因为我的负载是电容,不会有其它支路的电流。

调到VDD/2的主要目的是能够增加上下摆幅,但是增益是否增加还不确定。

只是仿真看着一样,因为没有别的通路当然一样

你这个最后接成反馈了吗?我看开路的话没有输出dc工作点啊。

跟这没关系,输出开路的话

直流电平Vout必然跟左边的M9/M11的漏端电压相等

对于共模响应来说,如果M9作为电流源输出阻抗足够高,那么无论你怎么变化vincom,输出的共模电平都应该是不太变化的,正如你DC扫描结果的前半部分所示。随着vincom增大到会使得M9退出饱和区的程度,输出共模电平才会随之有较大变化。

当vincom较小时,输出共模电平始终偏大说明输出级中M8的电流大于M6的电流(你在仿真中看到的电流当然是相等的,但如果此时所有参数不变,vout电压变成VDD/2,M8的电流就会大于M。你可以理解成在vout点加一个VDD/2的电压源再来看电流),所以你要实在想降低输出电平可以减小M8尺寸或者增大M6尺寸,不过你输出级增益很高,输出电平对这样的调节会很敏感。

即使你把输出电平调到了VDD/2,任何一点温度或工艺条件的变化都会显著影响这个结果,所以这个调节是没什么意义的。要真正理解这种电路通常使用在反馈系统中,输出电平由反馈自动调整,你考虑的问题其实只是一个offset的问题。

btw:用扫描共模DC响应的办法来找差模增益最大的偏置点,这太扯了。你这是共模放大器还是差模放大器啊