关键区域分析与存储器冗余

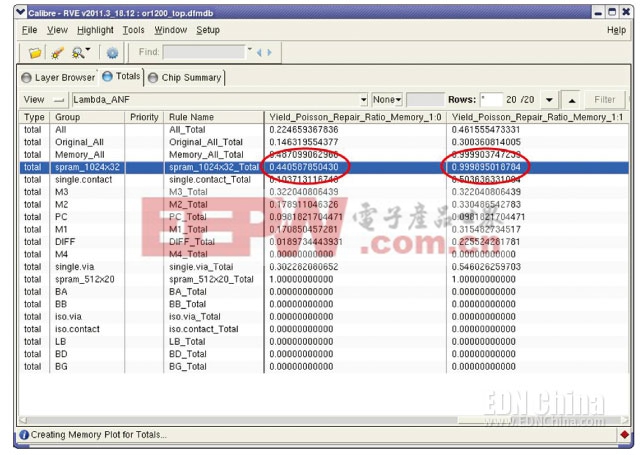

信息,Calibre计算出无冗余存储器的平均故障数,以及各种冗余配置。图1以表格的形式给出了结果,包括不同冗余配置的平均故障数。表中各行分别显示了整个设计(仅存储器),以及特定类型缺陷的结果。高亮的行表明1024×32位存储核心的平均故障率有显著改善;第6列的故障率是第5列的一半。为获得这种改进,第6列包含了一个冗余行,但增加第二个冗余行则几乎没有更多的改进(第7列)。

图1,用Calibre做的关键区域分析,显示出在不同配置情况下,存储器冗余对平均故障数的作用

图2列出了冗余方法对修复率的作用,分别按全部设计、所有分析层、存储器、块以及按层或群组。图3是一个工具创建的绘图,给出了各个冗余配置和各种类型缺陷的平均故障数。一个冗余行和一个冗余列相结合,就可大大减少平均故障数,而增加资源则没有什么更多的作用。从这些结果可以作出判断:预期的平均故障数取决于所考虑的存储器布局,以及晶圆厂与工艺的缺陷密度。现在,设计者就可以根据某个嵌入存储器的预期良品率,确定出各种冗余配置的效果。

图2,关键区域分析显示了针对很多参数的存储器修复率

图3,存储器图表示了各种存储器冗余配置的平均故障数。一个冗余行和一个冗余列相结合,就大大减少了平均故障数

存储器冗余旨在通过提高片芯良品率,从而降低制造成本。如果不采用冗余方法,提高片芯良品率的其它方式可能包括使设计更小型化,或减少缺陷率。如果在设计中无效益的部分使用冗余,那是浪费片芯面积和测试时间,增加了制造成本。在这两个极端之间,要根据充分的指导方针来确定是否增加冗余。有高缺陷率的设计可能需要较多的冗余;而低缺陷率的设计则可能不需要冗余。要量化良品率的改善以及确定最佳配置,有必要采用关键区域分析与精确的代工厂缺陷统计数据,对存储器冗余做分析。

- 线性电路分析——含受控源电路的网孔分析(01-23)

- 线性电路分析——网孔法详析(01-23)

- 线性电路分析——节点法详析(01-23)

- 线性电路分析——含受控源电路的节点分析(01-23)

- 含受控源的简单电路分析(01-26)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(05-12)