基于Matlab的FIR带通滤波器设计及DSP实现

摘要:借助Matlab的FDATOOL滤波器设计分析软件,设计了一种FIR数字带通滤波器,并对一段含噪语音信号进行滤波。利用汇编语言编程,在DSP上实现了该滤波器。实验结果表明,该数字带通滤波器精确,稳定性好,易于移植,具有很强的实用性与灵活性。

关键词:FIR数字带通滤波器;语音去噪;DSP;Matlab

0 引言

随着电子技术的飞速发展,人们正逐步进入数字化时代,数字滤波器越来越受到人们的关注,并且在近代电信设备和各类控制系统中的应用极为广泛,如语音处理、图像处理、通信、电视、雷达、生物医学信号处理等。数字滤波器根据其冲激响应函数的时域特性,可分为有无限长单位冲激响应(IIR)滤波器和有限长单位冲击响应(FIR)滤波器。IIR滤波器虽然可以利用模拟滤波器设计的结果,而模拟滤波器的设计有大量的图表可查,方便简单,但它的相位是非线性的。图像处理以及数据传输都要求信道具有线性相位,同时又可以具有任意的幅度特性。此外,FIR滤波器的单位冲激响应是有限长的,因而滤波器一定是稳定的。随着Matlab软件和信号处理工具箱的不断完善,可以利用Matl ab信号处理工具箱快速有效地实现数字滤波器的设计、分析和仿真。本文首先使用Matlab设计了一个FIR数字带通滤波器,并对一段含噪语音信号进行滤波,然后在TI公司生产的TMS320C5402芯片上具体实现了该滤波器。

1 FIR数字带通滤波器设计原理

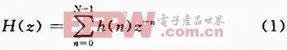

设FIR滤波器单位脉冲响应h(n)长度为N,其系统函数H(z)为:

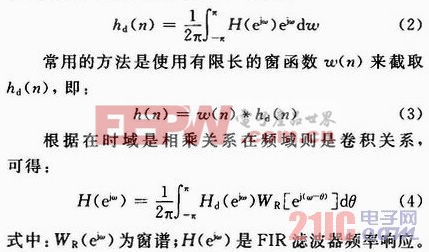

FIR滤波器的设计任务是选择有限长度的h(n),使传输函数满足技术要求。一般是先给定所要求的理想滤波器频率响应 ,导出hd(n)。因为理想滤波器的冲激响应hd(n)是无限长的非因果序列,而所要设计的是hd(n)是有限长的FIR滤波器,所以要用有限长序列hd(n)来逼近无限长序列h(n)。设:

,导出hd(n)。因为理想滤波器的冲激响应hd(n)是无限长的非因果序列,而所要设计的是hd(n)是有限长的FIR滤波器,所以要用有限长序列hd(n)来逼近无限长序列h(n)。设:

由此可见,窗函数不仅影响原信号在时域内的波形,而且也影响频域内的波形。

2 用Matlab辅助设计与仿真

设计一个FIR滤波器,关键是要得到正确的h(n)系数。把生成的滤波器系数加载到目标DSP程序中有两种方式:

(1)把滤波器系数输人到一个C语言的头文件,在所建工程中添加该头文件;

(2)直接把生成的滤波器系数加载到DSP程序的一个变量中。

本文采用第二种方法。选择菜单File→Export打开Export对话框,选择Coefficient File(ASCII),指定输出文件名,生成*fcf文件,就可以直接把生成的*fcf文件中的系数添加到DSP程序的变量中了。

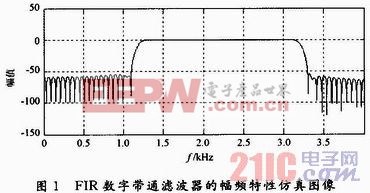

在Matlab软件平台下,利用wavread函数对语音信号进行采样,记住采样频率和采样点数。采样值放在向量y中,fS表示采样频率(单位:Hz),bits表示采样位数。根据语音信号的特点给出数字带通FIR滤波器的性能指标:设置通带频率fp1=1 200 Hz,fp2=3 000 Hz,阻带频率fs1=1 000 Hz,fs2=3 200 Hz,抽样频率fs=8 000 Hz,阻带最小衰减As=50 dB,通带最大衰减Ap=1 dB。这里采用窗函数设计法设计FIR带通滤波器。首先根据阻带衰减选择窗形状,海明窗和布莱克曼窗等窗函数均可提供大于50 dB的衰减。由于海明窗可提供较小的过渡带,所以选择海明窗。根据ωp1=2fp1/fs;ωs1=2fs1/fs,B(带宽)=ωp1-ωs1,N(窗口长度)=ceil(6.6/B),n(阶数)=N-1;算出阶数为132。在FDATo ol设计界面,按要求填写以上参数,得到FIR数字带通滤波器的仿真图像,如图1所示。

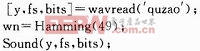

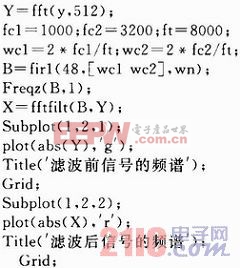

然后再用设计的FIR数字带通滤波器对加噪的语音信号进行滤波。在Matlab中,FIR滤波器利用函数fftfilt对信号进行滤波。编写Matlab程序如下,实现上述功能。

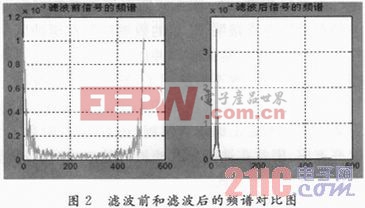

程序中“quzao”为录制的波形音频文件(.wav),对加噪的语音信号进行滤波仿真处理后,输出结果如图2所示。

3 FIR数字带通滤波器语音去噪的DSP实现

3.1 硬件结构

图3为FIR带通滤波器的语音去噪硬件结构框图。系统主要由DSP芯片(TMS320C5402)、A/D转换器(ADS7864)和D/A转换器(DAC7625)组成。

实现的核心器件采用TI公司生产的TMS320C5402芯片。该芯片采用先进的修正哈佛结构,片内共有8条总线、CPU、在片存储器、在片外围电路等硬件和高度专业化的指令系统,使它的处理速度和容量大大提高,为数字滤波中的复杂算法的实现提供了良好的保证。

A/D转换器采用TI公司生产的ADS7864芯片,它是一个高速(转换时间2μs)12位精度,6通道的A/D转换器件。它的最高工作频率可达8 MHz,采样率为500 kHz。根据奈奎斯特定理,信号的最高频率不能高于250 kHz,这样才不会有失真,而这个频率对于语音信号的处理已经足够。

D/A转换芯片采用DAC7625,它是一个4路12位D/A转换器件,每路都有输入寄存器和DAC寄存器,构成双缓冲结构,转换时间为10μs。

3.2 软件设计

3.2.1 数据组织方式

若输入信号x(n)和滤波器的单位冲激响应h(n)在频域分别为 ,则其输出信号的频率响应为

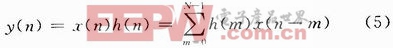

,则其输出信号的频率响应为 。根据离散傅氏变换的性质,可以得到滤波系统的差分方程:

。根据离散傅氏变换的性质,可以得到滤波系统的差分方程:

从上文Matlab的仿真过程可得到滤波器的级数N和滤波器系数h(n)。从上述可知数字滤波器实现时,主要是进行乘和加运算以及数据存取操作。

在定点DSP上实现FIR滤波有两种方式:一种是用线性缓冲区实现z-1,该方式能保证新老数据在存储器中的存放位置直接明了,新的数据存放在缓冲区的固定位置;另一种方式是循环缓冲区实现z-1,该方式新老数据在缓冲区的位置不直接明了,新的数据没有固定位置,但可以方便地完成滤波器窗口的自动更新。考虑到本方案中使用的是汇编语言编程,还有N的阶数较大,为提高速率,因此在选择FIR滤波器的方式时选择循环缓冲区实现z-1的方式。

对于N级的FIR滤波器,在数据存储器中开辟一个称之为滑窗的N个单元的缓冲区,滑窗中存放最新的N个输入样本。每次输入新的样本时,一新样本改滑窗中的最老数据,而滑窗中的其他数据不需要移动。利用片内BK(循环缓冲区长度)寄存器对滑窗进行间接寻址,环缓冲区地址首位相邻。

3.2.2 程序设计思路

程序设计的总体思路是:启动ADS7864对输入的模拟信号进行A/D转换,每采集到一个数据就送入DSP进行滤波运算,运算结果送DAC76 25转换为模拟量。不断地重复上述过程,在DAC7625的输出端就得到滤波后的模拟信号。

为了精确地控制ADS7864的采样率,使用TMS320C5402内部的定时器控制采样时间间隔T。设置定时器的定时时间等于采样时间间隔T,并让它工作在中断方式,则定时器每过T时间间隔就向CPU发出中断请求,CPU响应中断请求,转去执行中断服务程序。在中断服务程序中读取A/D转换结果,对转换结果进行滤波运算,并将运算结果送D/A转换器转换为模拟量。因此,程序分为主程序和定时器中断服务程序两部分,流程图如图4,图5所示。

- 基于Matlab的无失真模拟滤波器设计(04-19)

- 基于Matlab的IIR数字滤波器设计方法比较及应用(07-15)

- 基于Matlab的雷达系统仿真软件包设计与实现(09-16)

- 基于Matlab的FIR数字滤波器设计(10-07)

- 基于Matlab的孤立逆变电源设计方案(09-17)

- 13款逆变电源的设计技术及具体应用案例(07-07)