基于BF533和FPGA的雷达信号模拟器设计实现

时间:10-16

来源:互联网

点击:

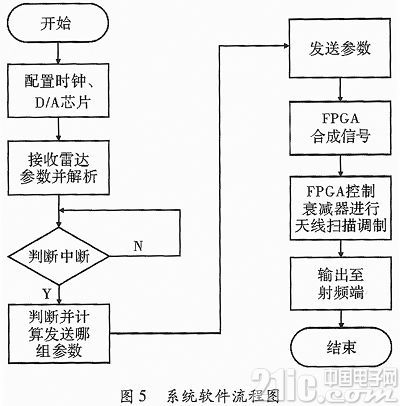

合成。系统软件流程图,如图5所示。

中断是DSP与FPGA之间通信的时序控制信号。在每个脉冲周期内,FPGA完成接收DSP通过总线发送的数据,立即给DSP发送中断信号,且通过总线发送一组二进制标志位,低4位有效。FPGA根据时序判断下一组信号的通道号,并将相应位置置位。DSP通过判断标志位来选择发送的雷达参数。

5 结束语

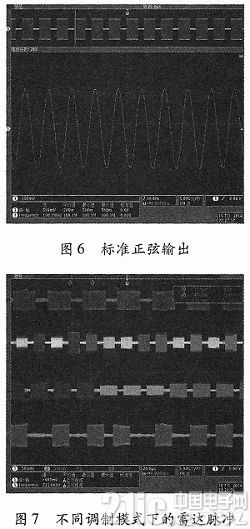

文中采用DSP与FPGA相结合的方式模拟雷达信号,并通过软件设置雷达参数。图6和图7为示波器上观测到的实际输出信号。图6为标准正弦输出信号,图7为独立的四通道在不同调制模式下的雷达脉冲。

如图7所示,第1通道为固定频率、固定PRI的脉冲信号;第2通道为频率捷变脉冲信号,可看到相邻脉冲之间频率不同,且变化无规律;第3通道为频率组变,每三个脉冲为一组,组间频率随机变化;第4通道PRI参差调制,每3个脉冲为一周期,组内PRI各不相同。

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)