针对Flash存储特性的航天器大容量固态存储技术

随着航天任务的不断丰富、航天探测技术的不断提高(如探测器种类增多,相机分辨率提高等),中国空间站等重大战略规划的逐步实施,空间科技数据的采集速度与存储总量需求大幅度攀升,对存储器的容量、吞吐速率、数据管理提出了更高的要求。

目前航天器所携带的固态存储器的基本存储介质以SDRAM和Flash为主,Flash读写速度较SDRAM慢、操作复杂,但因为基础工艺的区别,Flash的存储密度远远超过RAM系列产品,不需要刷新,功耗低,并且拥有非易失存储特性,在重量、功耗、可靠性极其敏感的航天应用上,Flash将保持巨大的生命力和发展潜力。

基于Flash的存储系统主要有固态硬盘和介质直接管理两种方式。前者目前广泛应用在笔记本、服务器等商用领域,在存储设备内部,通过FTL(flash transition Layer,闪存转换层)的转换,可处理SATA命令,但在硬件接口及软件系统方面照搬传统磁盘管理技术,对存储特性利用并不充分:硬件SATA接口标准无法满足Flash存储系统性能要求,成为瓶颈;以文件系统为代表的数据管理策略,大都考虑磁盘环境进行优化,Flash的优势无法充分体现。航天级应用需要采用介质直接管理的方式,针对Flash存储特性,从底层进行硬件结构设计,在满足任务的容量、速度、容错等关键需求的同时,尽量降低系统复杂度,逐步实现数据有效管理策略。

1 Flash器件的存储特性介绍

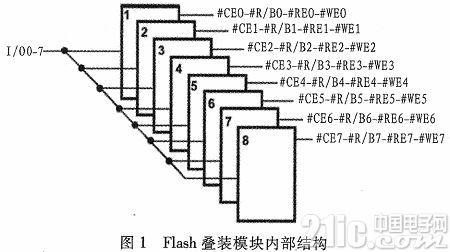

本文以3D—PLUS公司的NAND型32Gbits(4G×8)Flash叠装模块作为存储介质为例,介绍Flash存储特性。

1.1 并行性

该模块由8片4G位(512Mbits×8)SAMSUNG公司的NAND Flash芯片叠装而成,公用对外的8位宽I/O总线。该Flash芯片每2K字节的主存储区(Main Array)外加64字节的空余区(Spare Array)组成一页(Page),64页组成一个块(Block),4096块组成一个器件(Device)。

由于Flash存储模块的指令与数据公用I/O端口,对时序要求较为严格,但从应用的角度来看,由于各组I/O之间无依赖性,非常容易实现并行扩展。3D plus公司提供的存储模块通过简单的片选逻辑,即可封装多个Flash存储芯片。在航天实际任务应用中,我们也可以方便的通过并行总线技术,进行扩展,提高速度、提高容量。

1.2 最小操作单位及编程时间

写操作最小单位为“页”。写FLASH的过程分为两步,首先将命令、地址以及数据以字节方式写入芯片内部缓存(也就是“加载”,最快周期为50 ns)后,芯片内部需要一个内部编程的过程,才可以确定编程是否成功。典型时间tPROG为300μs,最大700μs。在编程过程中,芯片不响应外部命令,极大的降低了Flash的写入速度,是Flash应用的难点之一。

读操作通常也是以页为单位进行,但相对灵活些,也可以通过在输入地址过程中直接定位某一字节读取。在输入命令和地址后,需要一个等待时间tR后才可以将数据通过读脉冲读出。tR最大值为25μs。擦除操作必须以“块”为单位进行,每次必须同时擦除一个块内的全部64页的数据。在擦除的命令和地址输入后,需要等待时间tBERS后才可以确定擦除是否成功。tBERS的典型时间为2 ms,最大为3 ms。

1.3 无效块

NAND型FLASH芯片的特点是在出厂时就存在一定比例的无效块(Invalid Block),在芯片的使用过程中,有可能还会有新的无效块产生,具体表现为在编程或擦除过程中出现编程失败或擦除失败的情况。对无效块的读操作是允许的,但由于对无效块的写和擦除操作应尽量避免。坏块随机分布,难以从工艺上根本消除。

2 航天存储系统设计及应对技术措施

2.1 系统设计

文中以3D—PLUS公司的NAND型32Gbits(4Gbx8)Flash叠装模块作为存储介质,介绍航天实际应用的Flash存储128Gbits容量方案。存储控制采用FPGA集成全部控制模块,负责系统工作流程执行和状态维护。

在每次系统重新加电后,硬件电路将自动遍历整个存储区的簇使用记录信息,每64簇的簇使用信息组成一条块信息,全部块信息构成“块分配表”,即BAT(Block Assignment Table),包含Flash的当前使用信息,作为存储状态控制的依据。硬件初始化结束后,BAT表送往计算机内存,计算机软件在完成对CPU初始化设置后,进入常规任务管理,包括数据存储、数据回放、数据读取、数据擦除。FPGA与计算机通过

HPI总线通讯,计算机主板通过CAN总线与上位机通讯,实现指令遥控遥测等功能。存储控制实现以硬件为主,与地面通讯交互功能以软件为主。

为了保证存储数据可靠,实际应用中在存储控制模块中对存储数据进出Flash存储介质的端口进行RS编译码,有效检错、纠错,避免单粒子翻转造

固态存储器 Flash存储特性 并行总线 流水线 Flash存储系统 相关文章:

- 高速高精度流水线模数转换器的设计(12-09)

- 9位100 MSPS流水线结构A/D转换器的设计(02-11)

- 一种用于13 bit 40 MS/s流水线ADC中的采样保持电路设计(03-30)

- 流水线模数转换器的高精度低功耗采样保持电路(11-04)

- 适用于高速高精度流水线ADC的放大器(11-15)

- 10bit 60MsPs 15mW流水线ADC的设计(01-03)