10bit 60MsPs 15mW流水线ADC的设计

0 引言

模数转换器是现代数字通信系统中十分重要的单元。与模拟信号相比,数字信号具有便于存储、转移、保真度和可靠性高等优点。但是因为人们所处的世界是连续的模拟环境,其中所有(物理、化学、生物等)信号都是模拟的,这是数字电路无法直接处理的。因此,必须借助于ADC将从外部采集来的模拟信号转变成数字信号,才能由数字电路处理,然后再以适当的方式输出。随着无线通信系统和手持设备的快速发展,ADC的功耗已经成为ADC设计中的主要问题。特别是在移动电话、数码相机、手持存储设备等应用中,减小ADC的功耗已成为必然的趋势。本文通过对比较器进行特殊的处理,去掉了ADC中的采样保持电路,并且引入运放共享(op-amp shar-ing)技术,从而完成了一个分辨率为10bit、采样频率为60 MHz、功耗为15 mW的全差分流水线低功耗ADC的设计。

1 ADC第一级的设计

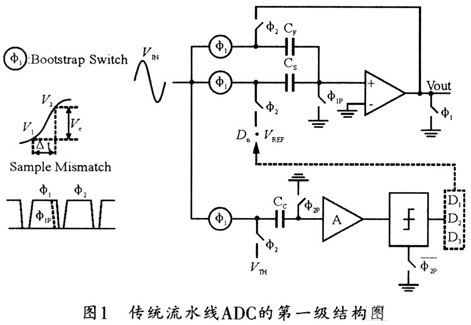

在传统流水线ADC结构中,为了减小MDAC和比较器之间时钟不匹配带来的动态误差,通常需要引入一个采样保持电路来保证MDAC和比较器具有同样的采样电平。虽然,采样保持器的引入可以很大程度的减小ADC的动态误差。但是,为保证整个ADC的精度,采样保持电路的精度必须高于ADC的要求。这就要求采样保持电路中的运放必须有足够高的增益和足够大的带宽,因此采样保持器就成为整个ADC功耗最大的一个模块,通常要消耗整个ADC器件1/5到1/4的功耗。

传统无采样保持电路ADC的第一级结构如图1所示。在ψ2时刻,比较器对阈值电压VTH进行采样,与此同时,MDAC处于对余量电压进行放大的状态。当ψ1到来时,MDAC和比较器同时对模拟输入信号进行采样。MDAC在ψ1P下降沿采到V2,但是由于比较器前置放大器存在一个△t的延时,所以比较器实际采到并决定输出比特值的电压是在ψ1P下降沿前△t时刻采到的V1。换一句话说,由于前置放大器存在延时,比较器采到的电压值要比V2早,故与V2存在一个Ve的差值。而Ve与输入频率、最大斜率等参数有关,其每级1.5 bit的传递函数如下式所示:

式中,Dn可取-1,0,1。它的误差容忍范围(即Ve的最大值)为1/4VREF。假设输入信号为Vin=VREFsin(2πfint),fin为其输入频率,那么,它的最大斜率可以表示为:

所以,△t时间的不匹配所引入的Ve可以表示为2πfinVREF△t。可见,输入越快,Ve越大。对于每级2.5 bit的ADC,Ve允许的最大值为1/8 Vref。

为了消除Ve,本设计中采用改进的ADC第一级结构,其电路如图2所示。其中比较器有两个分开的电容,在φ1时候,分别对信号和阈值电压VTH进行采样。φ1结束时,前置放大器有一段时间Tamp对φ1p下降沿采到的信号进行放大。这就避免了由于前置放大器延时所引入的△t,消除了Ve,因此也就提高了第一级电路的动态性能。

2 运放分享技术

流水线ADC是在两相非交叠时钟的控制下,使各流水线子级在采样和保持状态之间切换。流水线ADC相邻两级的控制时间是相反的,当前一级处于采样状态时,后一级处于保持状态。运放只有在保持状态时,才能真正被用到,在采样状态,运放实际处于重置状态,输出是短接的。所以,可以利用流水线ADC的这一特性,使相邻两级共用一个运放,从而减小功耗。

本设计采用4级2.5 bit加一个2 bit Flash的ADC结构。由于运放共享技术的引入,运放的数量从原来的4个减少到了2个,因而大大减小了功耗,优化了设计。其运放共享技术原理图如图3所示,与传统流水线ADC相比,它只是添加了开关ISO1租ISO2来对运放的输入进行切换。但开关ISO1和ISO2的引入又会引发其他问题,如ISO1和ISO2的开关电阻会加大信号通路的阻值,同时,这些电阻和寄生电容的结合会产生一个零点,而这会引起闭环电路的过冲和震荡。所以,必须对这些开关进行优化,以减小过冲并避免震荡。增加开关的尺寸可以减小开关的阻值,但是又会增加寄生电容,减小反馈系数,降低闭环的带宽,导致闭环速度降低。

3 运放的具体设计

在选取运放结构时,需要对运放增益、带宽、输出摆幅、速度、功耗和稳定性等方面进行综合考虑和折中。随着工艺尺寸的不断缩小和供电电压的不断降低,两级运放比单级运放具有更高的增益和输出范围。但是,在速度、功耗、共模反馈,特别是稳定性方面,两级运放也有着明显的缺陷。本设计中的信号输入范围为500mVpp,这样,折叠式运放(folded-cascode op-amp)已经足以满足摆幅的要求。但为了达到低功耗,高速度,高直流增益以及非常良好的稳定性,本设计在第一、二级所用的运放采用折叠式增益增强结构(gain

- 高速高精度流水线模数转换器的设计(12-09)

- 9位100 MSPS流水线结构A/D转换器的设计(02-11)

- 一种用于13 bit 40 MS/s流水线ADC中的采样保持电路设计(03-30)

- 流水线模数转换器的高精度低功耗采样保持电路(11-04)

- 适用于高速高精度流水线ADC的放大器(11-15)

- 适用于12 bit流水线ADC采样保持电路的设计(01-17)