10bit 60MsPs 15mW流水线ADC的设计

时间:01-03

来源:互联网

点击:

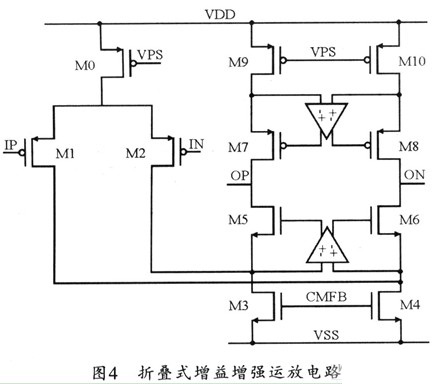

boosting)。其电路结构原理图如图4所示。

为了避免出现慢建立(slow settling)和不稳定,辅助运放的单位增益带宽ωadd必须满足:

βωμ<ωadd<ωp2 (3)

式中,ωμ表示主运放的单位增益带宽,ωp2表示主运放的次极点。

4 仿真结果

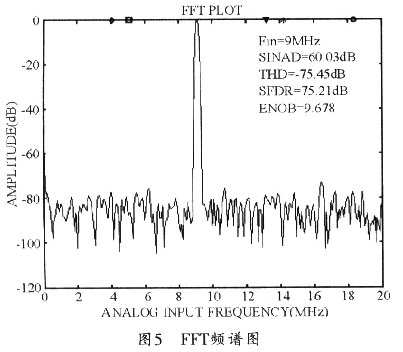

笔者在SMIC 0.13μm CMOS工艺下,对整个ADC进行了瞬态仿真。在60MHz采样频率下,其输入幅度为475mV的正弦信号。那么,在输入频率为9MHz时。即可得到图5所示的FFT频谱图。图中,信号的有效比特数(ENOB)为9.67bit,无杂散动态范围(SFDR)为75.2 dB。整个ADC的功耗为15 mW。可以满足模拟电路高线性度和低功耗的要求。

5 结束语

本文给出了一种高性能低功耗流水线ADC设计方法,它对比较器进行了特殊处理,并去除了采样保持电路,同时引入运放共享技术,使电路所需的运放数目比传统流水线ADC减少了一半,从而大大降低了功耗。该ADC电路在1.2 V供电电压下,采样率可达60 MHz,ENOB为9.67 bit,功耗为15 mW。

- 高速高精度流水线模数转换器的设计(12-09)

- 9位100 MSPS流水线结构A/D转换器的设计(02-11)

- 一种用于13 bit 40 MS/s流水线ADC中的采样保持电路设计(03-30)

- 流水线模数转换器的高精度低功耗采样保持电路(11-04)

- 适用于高速高精度流水线ADC的放大器(11-15)

- 适用于12 bit流水线ADC采样保持电路的设计(01-17)