针对Flash存储特性的航天器大容量固态存储技术

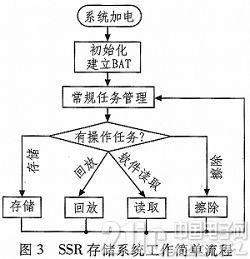

成存储数据错误,并提交检纠错信息至遥测工程参数。系统拥有回复出场初始化的命令,当检测到存储系统出现较为严重的异常时可以恢复存储系统至出场状态。同时可以增加存储电路板备份板,由复接器控制冷备或者热备,提高系统可靠性。

2.2 并行总线技术和“簇”的概念

叠装模块包含8片Flash芯片,公用对外的8位宽I/O总线。128 Gbits配置的存储区模块由4个Flash叠装模块构成,将4片Flash控制总线、状态总线互连,而I/O总线扩展为32位,其中4片Flash的8位宽I/O总线分别对应32位总线的不同数据位段。即4片并行的FLASH芯片相同地址的页被看作一个基本单位,即“簇”,因此1“簇”的基本存储空间为2 kx32 bits。经扩展后,一簇容量为64 kbits,64簇组成一个块(Block)。

4倍总线扩展的系统操作速度将提高为原来的4倍。同时可以非常简单的进行更多的扩展,但考虑到控制总线的驱动负载能力,更多的并行扩展可能带来时钟沿建立时间不稳定,可以使用总线驱动器增强驱动负载能力。

2.3 流水线技术

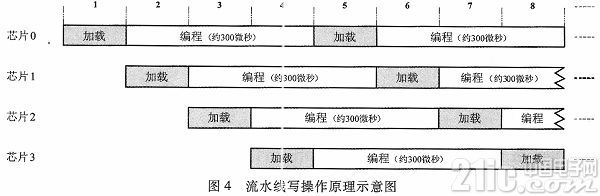

为了提高系统的存储速度,根据FLASH芯片的操作特点,在对存储区模块写入时还将采用流水线操作的方式。将多片FLASH分成若干组,每次加载(写)一页的数据到一组Flash芯片后,该组芯片总要有大约300μs的内部编程时间,在此期间尽管不能对该组芯片进行其它操作,但可以立即进行另一组芯片的加载。如果采用16 MHz的写时钟(周期62.5 ns),加载2k数据的时间大约为130μs左右,当第4组芯片加载完毕后,第一组芯片的编程过程通常已经结束,待系统确认后,开始下一个循环。根据写操作典型事件,本设计采用4级流水线写操作,便可以基本保证在宏观上实现对存储区的全速率无间断连续数据写入。图4为流水线写操作的原理示意图。

2.4 坏块管理

对于初始无效块,将被直接跳过,后续数据将被加载到该无效块在本流水级内后续的第一个有效块中。如果在使用过程中出现了新增的编程无效簇,该簇所处的块将被定义为程无效块,系统将把该块所在流水级内后续的第一个有效块作为替代块,编程出错的数据将被重新加载至替代块内的相同偏移页地址的簇地址空间,该流水级后续的数据将被加载到替代簇地址的后续地址中。

3 民用Flash存储系统的启示

民用Flash存储系统有两个特点,一是Flash存储介质随着半导体技术的提高密度增加很快,但由于工艺原因,对单粒子效应敏感,密度越大,可能造成的混乱越严重,不适用于航天环境。二是存储管理方式研究较为深入,极大的方便了用户使用,借鉴意义较大。

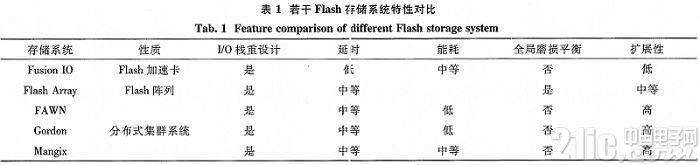

民用Flash存储系统管理类别较广,大体分为Flash加速卡、Flash存储阵列与分布式集群系统,大多关注3个关键技术,基于I/O栈调整与重构的存储性能优化、系统级可靠性、体积与能耗。代表性Flash存储系统对比见表1。而从航天存储系统现状来看,系统软件层的I/O栈优化尚无必要,而关注全局磨损平衡的系统级可靠性研究参考性较强,体积与能耗的相关考量也有相互借鉴的地方,分布式集群系统的设计思想有一定的启发性。

系统级可靠性研究中磨损平衡的提出,是由于Flash存储单元的多次擦除,会削弱其保存电子的性能,使得数据易受干扰。闪存的擦除次数在一万到十万次之间,并且随着存储密度增加而降低。民用存储系统一般在FTL内实现磨损平衡策略。动态磨损平衡在擦除与写入的过程中,综合考虑存储单元的磨损程度,实时进行平衡;静态磨损平衡则是定时交换读写频次低的冷数据与频次高热数据的存储位置,又可分为随机平衡机制,与基于擦写次数的平衡机制。

分布式集群存储系统的设计与航天应用的流水操作思想较为相似,都有着用空间换取速度的指导思想。不过前是从更高层次进行的整体系统设计,包括系统架构、FTL优化等措施,解决Flash接口速率远远小于数据吞吐速率需求的问题,但需要考虑大规模扩展带来的时延和可靠性问题。分布式集群存储系统突出特点是拥有良好的扩展性,优化存储状态更新查询方式、选择相适应的低频低功耗的CPU,有效降低整体功耗。

航天科技任务越来越丰富,科学数据的种类与数量不断增加,对存储系统数据管理要求也越来越高。相比于航天用存储系统硬件架构从磁带机、磁盘到固态存储器的多次升级,相应的数据管理研究与应用较为落后,如高效坏块管理、长时间在轨磨损平衡、适应航天综合电子平台的文件操作系统等。目前国内外民用基于Flash的固态存储系统架构与优化技术研究进展较快,也更为丰富,对航天应用具有较强的启发性。

4 结束语

针对Flash存储特性,本文以航天任务为背景,提出一种基

固态存储器 Flash存储特性 并行总线 流水线 Flash存储系统 相关文章:

- 高速高精度流水线模数转换器的设计(12-09)

- 9位100 MSPS流水线结构A/D转换器的设计(02-11)

- 一种用于13 bit 40 MS/s流水线ADC中的采样保持电路设计(03-30)

- 流水线模数转换器的高精度低功耗采样保持电路(11-04)

- 适用于高速高精度流水线ADC的放大器(11-15)

- 10bit 60MsPs 15mW流水线ADC的设计(01-03)