具有多个电压轨的FPGA和DSP电源设计实例

降压直流/直流转换器拓扑的回顾

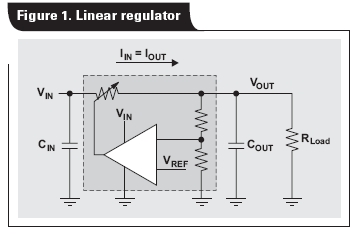

降压POL直流/直流转换器可以分成两类:线性稳压器和基于电感的开关稳压器。图1显示了线性稳压器的功能图。

线性稳压器的主要优点是芯片成本低、设计时间短,另外,由于带有内部开关并只需要一个输入和输出电容,所需要的板面积也比较小。另外,线性稳压器可以提供干净的低噪声输出电压。其主要缺点是效率低,在重负载时等于VOUT/VIN,导致产生数值为(VOUT–VIN) ??IOUT的功率耗散。功率以热的形式损失掉,而热又必须通过稳压器的封装和/或外部散热装置散发掉。在该市场上,由于目前大多数稳压器的最小输入电压为1.8到2.7V,线性稳压器非常适于负载电流较低而电压较高的电压轨。另一个缺点只出现在启动速度快但不可控的低成本简单稳压器中,这个问题本文将在后面予以讨论。

图2给出了同步降压开关稳压器的一个方框图。降压开关稳压器使用两个开关来产生工作周期等于VOUT/VIN的脉冲串。当负载变化时,该稳压器的反馈控制环通过调制固定频率脉冲串的脉冲宽度(或既调制脉冲频率也调制脉冲宽度)来不断调整电压,从而产生了 "脉冲调宽"(PWM)这个术语。然后,用感容滤波器(LC输出滤波)对方波脉冲串进行滤波,进而得到带有三角形输出电压纹波的直流输出电压。

|

不论采用固定频率还是可变频率的PWM,转换器的拓扑结构都对输出纹波产生影响。在负载变化范围内,固定频率PWM转换器的控制环使用带有负反馈环的偏差放大器通过调制脉冲宽度来调整输出电压。

|

这些稳压器的输出纹波等于电感纹波电流与输出电容的等价串联电阻(ESR)的乘积。因而,选择较大的电感(高于必需值)和ESR较小的输出电容可以降低输出纹波。然而, ESR低的输出电容将使反馈环更加难以补偿。幸好,电源芯片制造商们提供的电源设计软件可以极大地缩短固定频率PWM转换器的设计时间。大多数变频转换器的控制环包含带有时间或电压滞环的比较器,该比较器在输出电压低于或高于参考电压时把开关接通或断开。同固定频率转换器相比,由于其控制环有所简化,这些滞环转换器所需要的设计时间较短。另外,因为该比较器在输出下降到比较器的参考电压之下时几乎立即接通开关,同带有有限带宽控制环的固定频率转换器相比,滞环转换器对电流升高(暂态)的响应速度更快。然而,滞环转换器的运行需尽可能降低输出纹波。

同线性稳压器相比,开关稳压器的效率更高(典型值为85到95%),但通常芯片和支持元件的成本都较高、设计时间较长且板面积较大。同线性稳压器相比,开关稳压器的另一个缺点是开关噪声(如EMI)和输出纹波较大。通过仔细选择元件(如选用带有屏蔽的电感和低ESR的输出电容)和适当地布置电路板可以把开关噪声降下来。在开关频率可变时,滞环转换器可能会产生难以滤除的输出电压纹波和辐射。

然而,当输出电流较大、输入输出之间的差别较大或输入电源的功率受到限制时(如廉价的墙砖电源),只有开关转换器可以提供足够高的效率并降低功率热损失。

目前,市场上提供各种不同集成水平的降压开关转换器。插入式(Drop-in)模块的设计灵活性有限且成本偏高,但所需要的设计时间最少,仅仅需要一个输入和输出电容。在另一个极端是一些要求外部开关以及电感、滤波电容和补偿元件的控制器。这些控制器设计灵活性最高,如果付出足够的设计努力,可以成为性能价格比最高的方案,但所占用的板空间通常也最大。介于这两者之间的是集成型FET降压转换器,同控制器相比,所要求的板面积较小,设计灵活性也相对较小,而方案总成本也各不相同。同步式转换器/控制器的两个开关都使用晶体管来实现,因而同低侧开关使用二极管的转换器相比,通常效率更高,特别是在输出电压低于2V时。因而,要在线性稳压器、固定频率控制器/转换器或滞环控制器/转换器之间做出正确选择,需要综合考虑应用系统的要求以及效率、成本和尺寸等因素。

转换器输出电压的精度

大多数FPGA和DSP内核和I/O

- 实话实说电源设计(01-22)

- 通用电源设计指南(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 电源设计小贴士3:开关电源阻尼输入滤波器(02-03)

- 一种适合教学的开关电源设计及调试(09-06)

- 为您的电源选择正确的工作频率(10-29)