基于BF533和FPGA的雷达信号模拟器设计实现

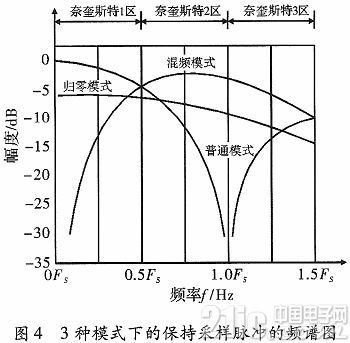

归零(RZ)模式和混频模式。这3种模式下的保持采样脉冲频谱图,如图4所示。

图4所示,对于普通模式而言,其保持采样脉冲的频谱图为sinc函数,且在Fs处衰减至最低,在与数字样本频谱相乘的过程中,可提取出信号的基频分量,而镜频分量则被有效抑制。但为得到中频频率分量,若使用普通模式,就需要再经过一个乘法器进行混频,进而得到所需的中频信号的分量。对于归零模式而言,其频谱在第1、2、3奈奎斯特区域均相对较为平滑,且在2Fs处衰减至最低,虽频谱相对较为平滑,但其整体而言增益较低,难以有效提取出所需的中频频率分量。而对于混频模式而言,从频谱图可看出,在奈奎斯特2区增益较大,且在0.75Fs处增益达到最大,从而可有效地抑制基频分量而增加镜频分量,并可直接提取出所需的中频频率分量,这相对于普通模式,便可省去混频的环节。由于本模拟器输出的是中频信号,其中心频率为960 MHz,因此文中选用混频模式。

3 模拟器雷达信号类型

从雷达辐射信号波形来看,各种技术体制的雷达选用的信号形式主要包括脉冲调幅信号、线性调频脉冲信号、相位编码脉冲信号等。在雷达信号环境仿真中,需建立雷达信号环境的仿真模型,其中包括雷达脉冲信号模型、天线扫描模型、多信号脉冲排序模型等。本模拟器系统可提供载波频率(RF)模型、脉冲重复间隔(PRI)模型和脉冲幅度(PA)模型。而对于所有的模型均可通过DSP软件计算实现。

3.1 RF模型

(1)固定载频雷达。对于该雷达,雷达发射脉冲序列的载频保持不变,RF模型为

RFi=RF,i=1,2,3… (1)

式中,RF为雷达脉冲载频的中心频率,其为一非时变的确定性常数。

(2)频率捷变雷达。对于该雷达,有两种捷变模式,即脉间捷变频和脉组捷变频模式。脉间捷变频模式采用捷变技术,使雷达每个脉冲的载频在一个较宽的频段上作随机的快速跃变。若频率捷变范围为△RF,则脉间捷变频雷达的RF模型为

其中,rand(i)是[0,M-1]之间的均匀分布整型伪随机数;M是捷变频点数。

脉组捷变频模式是指雷达脉冲的载频随机捷变是成组变化的。组内脉冲的载频相同,组间脉冲载频不同,且随机捷变。若频率捷变范围为△RF,则脉组捷变频雷达的RF模型为

其中,rand(i)是[0,M-1]之间的均匀分布整型伪随机数;M是捷变频点数;K是分组脉冲数;int(k)是取整函数。

(3)频率分集雷达。对于该雷达,其同时发射一组具有相同脉宽和重频的发射脉冲,这些脉冲的载频各不相同,设频率分集数为M,频率分集的频率集为

,则RF模型为

3.2 PRI模型

(1)重频固定雷达。对于重频固定雷达,雷达脉冲的脉冲重复间隔(PRI)保持不变,PRI模型为

PRIi=PRI,i=1,2,3… (5)

其中,PRI为一非时变的确定性常数。

(2)重频抖动雷达。对于该雷达,其PRI值一般是在一定范围内随机变化的。这种变化是随机的,但也可按一定舰律变化。其PRI模型为

PRIi=PRI0+δT,i=1,2,3… (6)

其中,PRI0为雷达信号PRI的中心值或平均值,δT是抖动量,其是在范围[-△PRI,+△PRI]内均匀分布的随机序列。△PRI与PRI的比值称为最大抖动量

式中,γ用以表现抖动的相对大小,其典型值为±1%~±10%。

(3)重频参差雷达。对于该雷达,重频参差雷达是一种具有多个重复频率的雷达。其参差方式一般有2参差、3参差等,最多则可能有16参差。但最常用2参差和3参差。对于具有M个PRI的雷达,PRI模型为

PRIi=PRIk,k=mod(i,M),i=1,2,3… (8)

其中,M为参差周期数,每经过M个脉冲,各参差PRI值循环变化一次。参差PRI脉冲列的总重复周期等于所有参差周期之和。

3.3 PA模型

由于仿真的信号环境与侦察系统内部无关,脉冲幅度可用到达侦察系统处的辐射源功率密度表示,这里取功率密度的对数作为脉冲幅度。设雷达信号功率为Pt,天线增益为Gt,侦察机与雷达之间的距离为R,电波大气传播损耗为L,则脉冲功率可表示为

式中,F(θ)为归一化的天线方向图函数。对处于跟踪状态下的雷达,F(θ)=1;而对处于搜索状态下的雷达,F(θ)受雷达波束形状和扫描方式的影响。在具体计算时,使用的脉冲幅度与上式的脉冲功率还需进行转换,将其转换成电压值使用。

4 模拟器的软件实现

在雷达模拟器的设计中,软件设计工作包括通过串行SPI接口编程配置时钟和D/A芯片;DSP通过总线与USB和FPGA进行通信;DSP内部进行数据处理;FPGA利用Verilog硬件描述语言,完成DDS的逻辑译码等工作。

DSP程序主要通过ADI公司提供的开发软件VisualDSP++进行编程,生成可烧写到Flash中的ldr文件。FPGA的编程用Xilinx公司的软件开发包ISE,实现信号

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)