小梅哥和你一起深入学习FPGA之数码管动态扫描

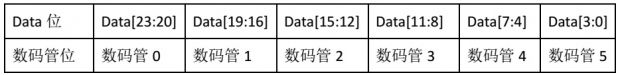

动采用了组合逻辑译码的方式进行,具体将在代码解读时讲解。 实验中还设计了一个控制器,该控制器主要通过读取按键信息来改变待数码管待显示的数据内容。 按键检测部分使用前一节开发的独立按键的驱动,因此这里不进行过多的分析介绍。 二、 关键代码解读 因为数码管属于低速设备,其正常的扫描频率为500~10KHz,扫描频率太快,会导致系统功耗增加,显示效果变暗。扫描频率太慢,会有明显的闪烁感。本实验通过调试观察,选择以1KHz作为扫描频率,实际显示效果非常好。 因此本实验首先就需要产生一个1KHz的扫描时钟,该时钟由系统时钟分频得到。产生1KHz扫描时钟的代码如下: 其中,定义了一个全局参数system_clk,该参数为Clk的频率,不同的时钟频率,只需要更改该参数,就可改变分频计数器的最大计数值,以保证1KHz分频的精准性。 在驱动中,数码管的位选以扫描时钟的速率进行切换,因为只有6位数码管,因此当位选计数到6-1后必须清零从头开始计数。相关代码如下: //位选信号控制 always@(posedgeclk_1K or negedge Rst_n) if(!Rst_n)sel_r<=3'd0; elseif(sel_r == 3'd5) sel_r<=3'd0; else sel_r<=sel_r+1'b1; 每个数码管需要显示的内容都不相同,由Data中相应的位指定,Data中各位与数码管的位对应关系如下: 因此需要从Data中将每个数码管被选中时需要显示的数据提取出来,提取数据的代码如下所示:

[color=rgb(51, 102, 153) !important]复制代码

电子 单片机 ARM FPGA 电路 电路图 二极管 发光二极管 三极管 LED 电阻 电流 仿真 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)