Xilinx FPGA入门连载62:基于SRAM批量读写的UART bulk测试

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

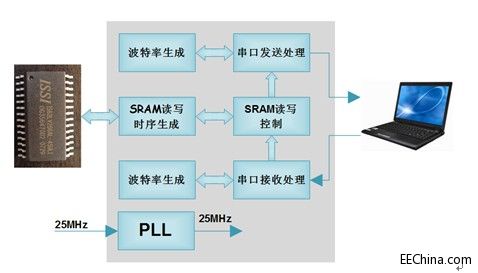

该实例的内部功能如图所示。

将SRAM分为128组(高7bit地址),每组256个数据(低8bit地址);上电初始对SRAM所有地址写入以其地址为首字节数据的递增数据;写入完成点亮LED[0]进行指示;等待UART接收到一个字节数据(有效数据为0-127),以此数据作为地址,读出该组256字节数据到FIFO中缓存,然后依次通过UART发送出去。

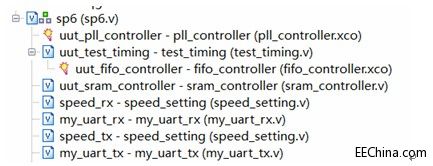

2 模块划分该工程实例的设计模块层次如图所示。

● my_uart_rx.v模块主要是完成数据的接收。

● speed_setting.v(speed_rx)模块主要响应my_uart_rx.v模块发出的使能信号进行波特率控制,并且回送一个数据采样使能信号。

● my_uart_tx.v模块在my_uart_rx.v模块接收好一个数据后启动运行,它将接收到的数据作为SRAM地址,读取SRAM对应地址的256个字节数据,然后通过UART发送数据返回给PC端,它的波特率控制是由speed_setting.v(speed_tx)模块产生。

● sram_controller.v模块产生SRAM的基本读写时序,直接控制SRAM的芯片接口。

● test_timing.v模块上电后产生SRAM遍历读写的控制信号、地址和数据,在接收到UART的读地址后,读取SRAM对应地址组的256个数据。

3 板级调试连接好下载线,给SP6开发板供电(供电的同时也连接好了UART)。

打开ISE,进入iMPACT下载界面,将本实例工程下的sp6.bit文件烧录到FPGA中在线运行。当我们看到D2指示灯亮起来的时候,说明FPGA已经完成了对SRAM所有地址的写数据初始化操作。接着我们可以使用串口调试助手读取SRAM数据了。

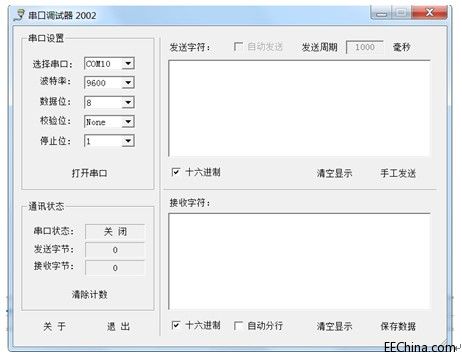

双击如图所示的“串口调试器”,。

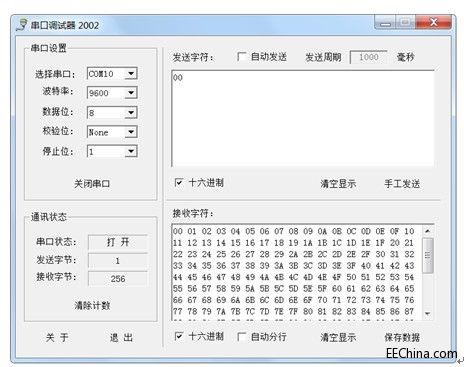

如图所示,打开串口调试器后,选择串口为COM10(我们前面在硬件管理器中新识别到的COM口,实验者应以自己电脑识别到的COM口为准),设置波特率为9600,数据位为8,校验位为None,停止位为1。点击“打开串口”。

如图所示,当我们点击完“打开串口”,其显示字符就变成了“关闭串口”;输入需要发送的数据“00”,然后点击按钮“手工发送”。随后我们便可以看到从16进制00开始递增的一串数据(一共256个)出现在了“接收字符”中。

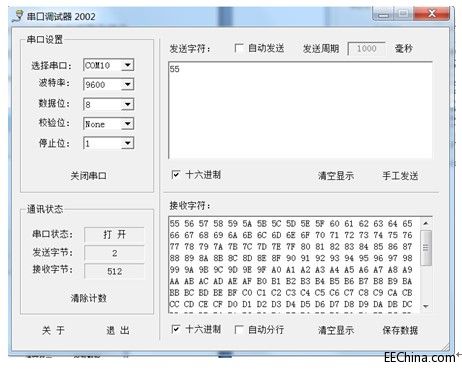

如图所示,若我们发送16进制数据55,则收到的数据是以16进制55打头开始递增的数据。我们往SRAM地址组写入数据的规则是,从和地址一样的数据开始递增的数据。大家可以再试试别的地址(地址有效范围是16进制的00到7F),看看是否都是符合我们的规则。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)