选择合适的SoC FPGA体系结构的重要性

时间:02-26

来源:互联网

点击:

集成降低功耗

新电子应用对功耗的要求越来越高——不仅仅是手持式设备,而且还有汽车应用,甚至是服务器机架等,这些都有很大的功耗和散热预算。SoC FPGA器件是可行的解决方案,帮助嵌入式开发人员实现其功耗预算。

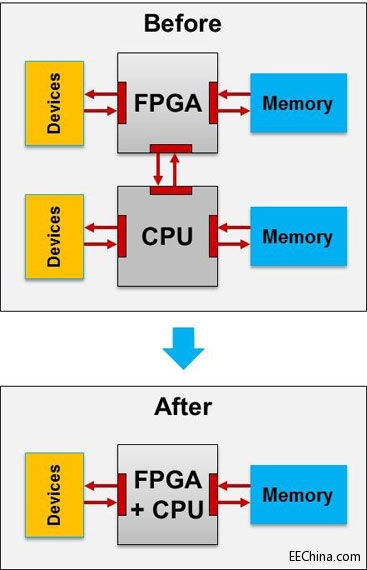

如图3所示,在一片SoC FPGA中集成处理器和FPGA组件能够把系统功耗降低10%到30%。I/O在器件之间传送信号,通常需要较高的电压,是应用中最耗能的组件。

图3.在一片SoC FPGA中集成处理器和FPGA,共享外部存储器接口,减少了高功耗的芯片间I/O连接。

简单的集成不但降低了功耗,Cyclone V SoC还具有时钟选通和调整等低功耗模式。处理器和FPGA还有独立的电源平面,支持应用程序完全关断FPGA供电,而保持处理器工作,监视任何中断。

为优化功耗,SoC设计与电源设计的关系越来越密切。在系统级,电源供电设计有时候要比SoC器件本身功耗更大。这些系统的难点在于怎样在减小电源供电布局和提高供电效率之间达到均衡。有很多电源供电选择为Cyclone V SoC提供支持,高级DC-DC电源转换器技术也为其提供支持,支持设计人员满足严格的功耗预算和空间限制要求。Altera提供Enpirion电源模块新产品,非常适合满足基于SoC FPGA的嵌入式系统的空间和效率限制要求。

熟悉的开发工具支持SoC FPGA

集成了前沿ARM应用处理器和FPGA架构的新一类SoC器件,能够以更低的成本,更迅速的实现低功耗电子产品,打开了新的应用空间。但是,伴随着硬件创新,FPGA工具、片内调试、软件调试和分析工具也应该不断创新。软件最终决定了设计人员能否成功的使用这些器件。为实现更广泛的应用,软件开发人员必须找到合适的SoC FPGA,掌握其特性,就像独立处理器软件开发那样轻松高效的使用它们。

来自Altera的SoC FPGA由SoC嵌入式设计套装(EDS)提供支持,套装包括全套的ARM兼容工具包,支持在Altera SoC器件上开发嵌入式软件。它包括开发工具、实用工具程序、运行时软件,以及应用实例,帮助您迅速开始SoC嵌入式系统的固件和应用软件开发。Altera和ARM之间这种非常重要的关系导致SoC EDS提供了独特的Altera版ARM Development Studio 5 (DS-5)工具包。ARM DS-5高级多核调试功能与FPGA自适应功能相结合——能够立即看到FPGA硬件中的改动,无缝链接至Altera的SignalTap逻辑分析器,这一SoC EDS工具包帮助嵌入式软件开发人员获得了前所未有的全芯片可视化和控制能力。

当调试出现问题时,开发团队必须能够确定这是硬件还是软件问题。支持Altera SoC FPGA的工具实现了处理器子系统和FPGA子系统之间代码和波形的交叉触发,或者从波形到代码的触发,很容易找到导致这些问题的原因。结果,开发团队能够找到并跟踪系统中某一状态是怎样出现的,为什么出现。交叉触发、跟踪和全局时间戳是IP验证、定制驱动开发以及工程中系统集成部分非常重要的特性。

除了找到故障位置之外, SoC EDS还帮助嵌入式系统开发人员知道系统为什么会进入这种故障状态,是怎样进入的。ARM系统跟踪模块(STM)支持跟踪基于CPU的软件事件。当系统执行时,应用软件可以发出硬件和软件事件“探测”信号,以监视系统行为,深入探查其工作。在“FPGA自适应”调试环境中,STM支持CPU和FPGA域的事件监视,不要求系统停止工作。

未来的SoC FPGA路线图

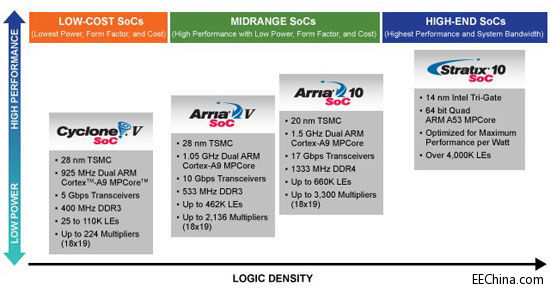

当选择SoC FPGA时,必须确定供应商的产品路线图.如图4所示,从长期看,这将保持您的系统竞争力,支持软件前向移植。开始时,所有硅片发展路线图的基础都是硅片工艺技术。目前Altera提供的Cyclone V和Arria V SoC采用了28 nm低功耗工艺制造,帮助工业、汽车、医疗和通信等对功耗要求较高的应用降低了功耗。

Altera的下一代Arria 10 SoC优化了中端应用的性能,提高了功效,减小了外形封装,降低了成本,适合多种中端无线基础设施、广播、军事,以及计算机和存储应用。Arria 10 SoC基于TSMC的20 nm工艺技术,结合了双核Cortex-A9处理器系统和业界领先的可编程逻辑技术。实现双核Cortex-A9处理器系统简化了第一代SoC FPGA的软件移植,尺寸更小的工艺技术将性能提升至1.5 GHz。

在先进通信、军事和数据中心应用中,第三代Stratix 10 SoC将进一步突破性能和带宽。Stratix 10 SoC基于Intel 14nm三栅极工艺技术,具有64位四核ARM Cortex-A53处理器。Cortex-A53支持32位兼容模式,如果需要,很容易实现现有软件的移植。

图4.Stratix 10 SoC是Altera的第三代SoC,采用Intel的14 nm三栅极工艺技术,集成了四核Cortex-A53处理器。

SoC FPGA是功能强大的新一类可编程器件,适用于多种电子设计。最流行的商用器件集成了标准ARM双核Cortex-A9——具有丰富的外设、片内存储器、高速内部互联体系结构、分层片内存储器,还有前沿的FPGA架构。创新软件设计和调试工具支持开发人员同时查看并交叉触发芯片的两部分(处理器和FPGA)组成。市场上的这些器件表面上看起来非常相似,但实际上底层体系结构却不尽相同。

Altera SoC 嵌入式 FPGA 电路 ARM Cortex 总线 电子 电压 电源模块 相关文章:

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 智能命令行设计及其在 SOPC 系统中的应用(08-14)

- 我的FPGA学习历程(05-23)

- 在FPGA中实现源同步LVDS接收正确字对齐(05-01)

- Altera FPGA下载配置(11-11)