选择合适的SoC FPGA体系结构的重要性

时间:02-26

来源:互联网

点击:

作者:Altera公司SoC产品高级市场经理Todd Koelling

在大部分嵌入式系统中,处理器和现场可编程门阵列(FPGA)完成最繁重的工作。处理器和FPGA通常单独工作,如果两种技术能够一起出色的协同工作,将形成功能更强大的嵌入式计算平台。在这些系统中,处理器一般提供高级管理功能,而FPGA完成严格的实时操作,大量的数据处理,或者处理器不太容易支持的接口功能。

SoC FPGA器件在一个器件中成功集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信,等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA的优点。

与以前的器件设计相比,SoC FPGA的功能和性能相当甚至是更好,但是减小了电路板面积,降低了功耗和系统成本——高达50%以上。通过在一个硅片上集成这些技术,系统开发人员避免了塑料封装的成本问题。如果设计中的CPU和FPGA使用分立的外部存储器,那么,设计人员应该将这些合并到一个存储器件中,进一步降低系统成本和功耗,减小电路板面积。处理器和FPGA之间的信号现在是在同一个硅片中,它们之间通信消耗的能耗要比使用分立芯片低很多。而且,处理器和FPGA之间有数千路内部连接,与两芯片解决方案相比,集成解决方案能够有效的提高带宽,降低延时。

嵌入式开发人员在为自己的应用选择最佳SoC FPGA时,需要考虑很多设计问题和工程决定。这些选择标准包括系统性能、系统可靠性、功耗、开发工具和未来发展路线图等。

采用SoC FPGA提高系统性能

最终,SoC FPGA中的系统性能是由能否在四个主要SoC功能之间高效移动数据来决定的,即,处理器、FPGA逻辑、互联,以及片内和片外存储器。

在各种应用中,系统性能主要是由数据通路性能决定的,器件应能够以“线速”处理连续数据流,很少出现失速或者中断。在这些应用中,FPGA逻辑处理关键数据通路,而处理器对控制通路进行高级管理。处理器解释一小部分到达数据,尽量不参与数据通路的工作。

为完成这种协调的合作,现代SoC FPGA采用了ARM双核Cortex-A9应用处理器,集成到高级28nm FPGA架构中。与其他应用处理器相比,Cortex-A9非常理想的同时实现了低功耗、功能、带宽和性能。

专门设计了Cyclone V SoC中的互联,FPGA逻辑和处理器之间的吞吐量高达100 Gbps以上,从而提高了系统性能,图1。FPGA逻辑和Cortex-A9处理器之间的100 Gbps互联保证了系统有足够的互联性能,支持大吞吐量数据流。

图1.Cyclone V SoC,FPGA和处理器之间>100 Gbps互联

能够有效的访问片内和片外存储器也使得SoC FPGA提高了系统性能。Cyclone V SoC中的硬核存储器控制器采用了复杂算法,尽可能提高您存储器的效率。这些算法使用缺陷权重罗宾带等复杂算法,管理会话优先级、对命令和数据重新排序、调度未完成的会话,从而提高了存储器带宽。其他的性能源自通过软件定制存储器控制器,与定制数据指标非常符合。

评估存储器控制器性能时,重要的是不仅仅要关注总线宽度和速度。LMbench等系统级基准测试适用于查看存储器子系统的总体性能。在667MHz Cyclone V SoC系统上运行LMbench基准测试表明,具有智能存储器控制器的Cyclone V SoC的存储器带宽更高——比竞争SoC器件高出17%,而且存储器工作频率降低了25%。这种在效率上的优势支持Cyclone V SoC以更低的时钟速率实现更大的带宽,降低了系统功耗。

采用SoC FPGA提高系统可靠性

随着存储器容量的不断增长,对错误探测和纠正的需求已经成为当今设计的发展趋势。大部分现代系统包括专用硬件来帮助实现数据完整性。这包括纠错码(ECC)保护——不仅仅是存储器控制器的一部分,而且还集成在处理器的片内存储器、高速缓存、外设缓冲以及FPGA中。错误检查和纠正电路使系统更可靠,系统不受意外数据错误或者数据损坏的影响。

存储器保护是通常与高级处理器中的存储器控制器相关的特性,称之为存储器管理单元(MMU)或者存储器保护单元(MPU)。处理器的存储器保护单元防止了错误或者非法的处理器会话读取甚至损坏其他存储器区。在Cortex-A9处理器中,ARM的TrustZone技术扩展了这一保护概念,为安全敏感的系统提供了系统级方法。

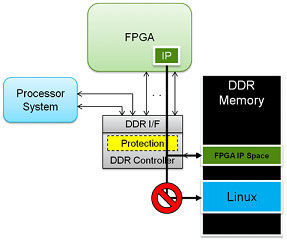

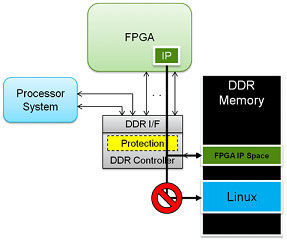

使用Cyclone V SoC,为操作系统和嵌入式应用软件指定了特定的存储器区域,而其他存储器区域可以专门用于基于FPGA的功能,如图2所示。通过存储器保护,FPGA主机功能不会损坏操作系统或者嵌入式软件区域。

图2.SoC应用中的DDR存储器保护,处理器和FPGA共享公共的存储器。

在大部分嵌入式系统中,处理器和现场可编程门阵列(FPGA)完成最繁重的工作。处理器和FPGA通常单独工作,如果两种技术能够一起出色的协同工作,将形成功能更强大的嵌入式计算平台。在这些系统中,处理器一般提供高级管理功能,而FPGA完成严格的实时操作,大量的数据处理,或者处理器不太容易支持的接口功能。

SoC FPGA器件在一个器件中成功集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信,等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA的优点。

与以前的器件设计相比,SoC FPGA的功能和性能相当甚至是更好,但是减小了电路板面积,降低了功耗和系统成本——高达50%以上。通过在一个硅片上集成这些技术,系统开发人员避免了塑料封装的成本问题。如果设计中的CPU和FPGA使用分立的外部存储器,那么,设计人员应该将这些合并到一个存储器件中,进一步降低系统成本和功耗,减小电路板面积。处理器和FPGA之间的信号现在是在同一个硅片中,它们之间通信消耗的能耗要比使用分立芯片低很多。而且,处理器和FPGA之间有数千路内部连接,与两芯片解决方案相比,集成解决方案能够有效的提高带宽,降低延时。

嵌入式开发人员在为自己的应用选择最佳SoC FPGA时,需要考虑很多设计问题和工程决定。这些选择标准包括系统性能、系统可靠性、功耗、开发工具和未来发展路线图等。

采用SoC FPGA提高系统性能

最终,SoC FPGA中的系统性能是由能否在四个主要SoC功能之间高效移动数据来决定的,即,处理器、FPGA逻辑、互联,以及片内和片外存储器。

在各种应用中,系统性能主要是由数据通路性能决定的,器件应能够以“线速”处理连续数据流,很少出现失速或者中断。在这些应用中,FPGA逻辑处理关键数据通路,而处理器对控制通路进行高级管理。处理器解释一小部分到达数据,尽量不参与数据通路的工作。

为完成这种协调的合作,现代SoC FPGA采用了ARM双核Cortex-A9应用处理器,集成到高级28nm FPGA架构中。与其他应用处理器相比,Cortex-A9非常理想的同时实现了低功耗、功能、带宽和性能。

专门设计了Cyclone V SoC中的互联,FPGA逻辑和处理器之间的吞吐量高达100 Gbps以上,从而提高了系统性能,图1。FPGA逻辑和Cortex-A9处理器之间的100 Gbps互联保证了系统有足够的互联性能,支持大吞吐量数据流。

图1.Cyclone V SoC,FPGA和处理器之间>100 Gbps互联

能够有效的访问片内和片外存储器也使得SoC FPGA提高了系统性能。Cyclone V SoC中的硬核存储器控制器采用了复杂算法,尽可能提高您存储器的效率。这些算法使用缺陷权重罗宾带等复杂算法,管理会话优先级、对命令和数据重新排序、调度未完成的会话,从而提高了存储器带宽。其他的性能源自通过软件定制存储器控制器,与定制数据指标非常符合。

评估存储器控制器性能时,重要的是不仅仅要关注总线宽度和速度。LMbench等系统级基准测试适用于查看存储器子系统的总体性能。在667MHz Cyclone V SoC系统上运行LMbench基准测试表明,具有智能存储器控制器的Cyclone V SoC的存储器带宽更高——比竞争SoC器件高出17%,而且存储器工作频率降低了25%。这种在效率上的优势支持Cyclone V SoC以更低的时钟速率实现更大的带宽,降低了系统功耗。

采用SoC FPGA提高系统可靠性

随着存储器容量的不断增长,对错误探测和纠正的需求已经成为当今设计的发展趋势。大部分现代系统包括专用硬件来帮助实现数据完整性。这包括纠错码(ECC)保护——不仅仅是存储器控制器的一部分,而且还集成在处理器的片内存储器、高速缓存、外设缓冲以及FPGA中。错误检查和纠正电路使系统更可靠,系统不受意外数据错误或者数据损坏的影响。

存储器保护是通常与高级处理器中的存储器控制器相关的特性,称之为存储器管理单元(MMU)或者存储器保护单元(MPU)。处理器的存储器保护单元防止了错误或者非法的处理器会话读取甚至损坏其他存储器区。在Cortex-A9处理器中,ARM的TrustZone技术扩展了这一保护概念,为安全敏感的系统提供了系统级方法。

使用Cyclone V SoC,为操作系统和嵌入式应用软件指定了特定的存储器区域,而其他存储器区域可以专门用于基于FPGA的功能,如图2所示。通过存储器保护,FPGA主机功能不会损坏操作系统或者嵌入式软件区域。

图2.SoC应用中的DDR存储器保护,处理器和FPGA共享公共的存储器。

Altera SoC 嵌入式 FPGA 电路 ARM Cortex 总线 电子 电压 电源模块 相关文章:

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 智能命令行设计及其在 SOPC 系统中的应用(08-14)

- 我的FPGA学习历程(05-23)

- 在FPGA中实现源同步LVDS接收正确字对齐(05-01)

- Altera FPGA下载配置(11-11)