在FPGA中实现源同步LVDS接收正确字对齐

时间:05-01

来源:互联网

点击:

在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Word Aligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。那么,如何FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐呢?在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(WordAligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。对于标准协议,FPGA通常都会有知识产权(IP)模块提供。本文主要讨论在FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐的设计方法及步骤。

LVDS已经成为业界高速传输最普遍应用的差分标准。LVDS的优势包括:由于采用差分信号带来的对共模噪声的免疫能力,进而提高了抗噪声能力;功率消耗较小,噪声较小等。由于LVDS有比较好的抗躁声特性,它可以采用低至几百毫伏的信号摆幅,进而可以支持更高的数据速率。

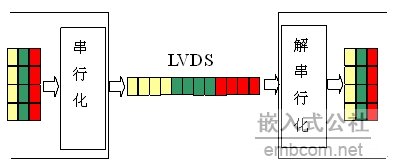

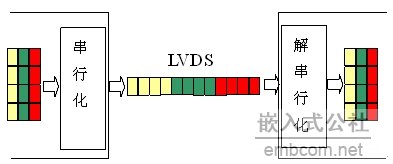

LVDS串行器/解串器(SERDES)可以完成多位宽度的并行信号到LVDS串行信号的转换以及反方向操作,如图1所示。有些器件提供图1中的随路时钟,但有些器件可能并不提供,这时LVDS解串器还必须具有时钟恢复(CDR)功能。市面上有各种规格的LVDSSERDES器件,此外FPGA或其它一些器件也都能集成LVDS SERDES模块。

另外一些相对低速的LVDS接口也利用低频的源同步时钟来携带字对齐信息,以便在接收端实现正确的数据恢复。这里的低频源同步时钟也如图1中的随路时钟,LVDS数据和随路时钟之间的倍数关系通常等于LVDS串行化时的倍数因子。比如,德州仪器(TI)的SN65LVDS95LVDS发送器,不仅可完成21:3的LVDS串行化发送,还将21位的并行数据和时钟串行化成3路LVDS数据输出和1路时钟输出。串行化因子的值等于7,所以输出时钟的频率是LVDS数据速率的七分之一。通过这个随路时钟,配套的解串器SN65LVDS96就能够正确恢复并行数据。

与这类单独的LVDS SERDES器件相比,FPGA集成LVDS模块能提供更高的集成度,并简化硬件设计、节省PCB面积,从而降低应用成本。高端FPGA还在I/O单元里固化了LVDS串行器/解串器,支持非常高的速率,比如Altera公司的Stratix III系列。

StratixIII FPGA系列是Altera公司基于TSMC65nm工艺的高端FPGA,是业界高密度高性能可编程逻辑器件中,功耗最低的产品系列。Stratix III器件可以同时提供最多276对LVDS串行化发送模块和276对LVDS解串行化接收模块,每路LVDS最高可以支持1.6Gbps。此外,它还独家提供可编程的输出摆幅和预加重功能,以支持长距离背板传送,如图4所示。

LVDS已经成为业界高速传输最普遍应用的差分标准。LVDS的优势包括:由于采用差分信号带来的对共模噪声的免疫能力,进而提高了抗噪声能力;功率消耗较小,噪声较小等。由于LVDS有比较好的抗躁声特性,它可以采用低至几百毫伏的信号摆幅,进而可以支持更高的数据速率。

LVDS串行器/解串器(SERDES)可以完成多位宽度的并行信号到LVDS串行信号的转换以及反方向操作,如图1所示。有些器件提供图1中的随路时钟,但有些器件可能并不提供,这时LVDS解串器还必须具有时钟恢复(CDR)功能。市面上有各种规格的LVDSSERDES器件,此外FPGA或其它一些器件也都能集成LVDS SERDES模块。

图1:LVDS串行器/解串器的功能示意图。

图2:字顺序得到保留。

图3:字顺序没有得到保留。

另外一些相对低速的LVDS接口也利用低频的源同步时钟来携带字对齐信息,以便在接收端实现正确的数据恢复。这里的低频源同步时钟也如图1中的随路时钟,LVDS数据和随路时钟之间的倍数关系通常等于LVDS串行化时的倍数因子。比如,德州仪器(TI)的SN65LVDS95LVDS发送器,不仅可完成21:3的LVDS串行化发送,还将21位的并行数据和时钟串行化成3路LVDS数据输出和1路时钟输出。串行化因子的值等于7,所以输出时钟的频率是LVDS数据速率的七分之一。通过这个随路时钟,配套的解串器SN65LVDS96就能够正确恢复并行数据。

与这类单独的LVDS SERDES器件相比,FPGA集成LVDS模块能提供更高的集成度,并简化硬件设计、节省PCB面积,从而降低应用成本。高端FPGA还在I/O单元里固化了LVDS串行器/解串器,支持非常高的速率,比如Altera公司的Stratix III系列。

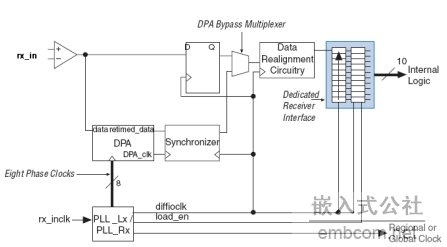

StratixIII FPGA系列是Altera公司基于TSMC65nm工艺的高端FPGA,是业界高密度高性能可编程逻辑器件中,功耗最低的产品系列。Stratix III器件可以同时提供最多276对LVDS串行化发送模块和276对LVDS解串行化接收模块,每路LVDS最高可以支持1.6Gbps。此外,它还独家提供可编程的输出摆幅和预加重功能,以支持长距离背板传送,如图4所示。

图4:Stratix III 支持可编程的输出摆幅(Vs(p-p))和预加重(Vpp(p-p))。

图5:Stratix III I/O固化的LVDS接收器。由于FPGA具有非常高的灵活性,比如支持不同LVDS输入数据和输入时钟之间的倍频关系,以及不同的解串行化因子,所以Str

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)