在FPGA中实现源同步LVDS接收正确字对齐

时间:05-01

来源:互联网

点击:

atix IIILVDS硬核模块的输出字顺序通常是不确定的,每次上电或者复位后字顺序都有可能发生变化,使用时需要根据特殊码型进行字对齐处理。

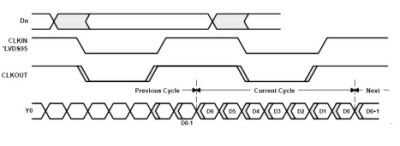

当输入到FPGA的数据和时钟之间的倍数关系等于解串器的解串行化因子时,FPGA与单独的LVDS解串器一样,有确定的字顺序输出,可以在没有训练码型的情况下继续正常应用。图6是解串行化因子为7时的时序图。假设随路时钟的上升沿对应数据的最高比特,在FPGA内部,PLL会从随路时钟产生一个进行过相位调整的7倍频率采样时钟。此时钟对输入数据进行采样后送入解串器,通过控制解串器的装载时钟相位,得到确定的并行数据输出字顺序。装载时钟的相位相对随路时钟相位的固定差异是通过接收PLL的相位控制来实现的,因此必须在输入时钟稳定后再释放PLL的复位控制,或者等输入时钟稳定后再复位PLL一次,否则输出的字顺序在每次上电时都可能不固定。

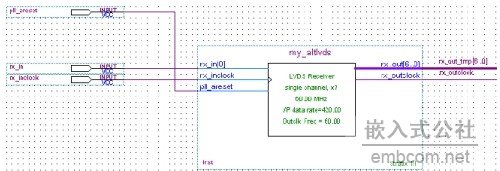

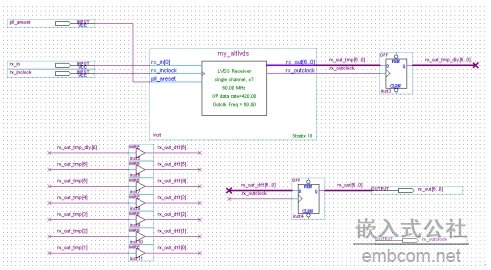

首先根据LVDS95的时序进行Stratix III中的LVDS模块(ALTLVDS)的调用。

接下来需要通过仿真找出串行因子等于7的情况下,LVDS硬核的字顺序情况。图11给出了顶层设计例子,图12是在MODELSIM里的仿真结果。

在利用StratixIII做LVDS接收时,我们可以将解串行化因子设置成等于输入的LVDS数据和时钟之间的倍数关系,这样就可以得到确定的字输出顺序,从而可以不依赖训练码实现正确LVDS接收的字对齐。此方法不仅适合于FPGA与单独的LVDS发送器进行对接,也可用于FPGA与FPGA之间的数据传送,使用时FPGA的LVDS发送端送出低频的源同步时钟即可。

当输入到FPGA的数据和时钟之间的倍数关系等于解串器的解串行化因子时,FPGA与单独的LVDS解串器一样,有确定的字顺序输出,可以在没有训练码型的情况下继续正常应用。图6是解串行化因子为7时的时序图。假设随路时钟的上升沿对应数据的最高比特,在FPGA内部,PLL会从随路时钟产生一个进行过相位调整的7倍频率采样时钟。此时钟对输入数据进行采样后送入解串器,通过控制解串器的装载时钟相位,得到确定的并行数据输出字顺序。装载时钟的相位相对随路时钟相位的固定差异是通过接收PLL的相位控制来实现的,因此必须在输入时钟稳定后再释放PLL的复位控制,或者等输入时钟稳定后再复位PLL一次,否则输出的字顺序在每次上电时都可能不固定。

图6:LVDS接收及解串行化时序图。

图7:LVDS95输出时序。

图8:综合设置页面。

首先根据LVDS95的时序进行Stratix III中的LVDS模块(ALTLVDS)的调用。

图9:频率和锁相环设置页面。

图10:接收器设置页面。

接下来需要通过仿真找出串行因子等于7的情况下,LVDS硬核的字顺序情况。图11给出了顶层设计例子,图12是在MODELSIM里的仿真结果。

图11:顶层模块的设计。

图12:仿真波形。

图13:字顺序的调整逻辑。

图14:内容为计数器的仿真输出波形。

在利用StratixIII做LVDS接收时,我们可以将解串行化因子设置成等于输入的LVDS数据和时钟之间的倍数关系,这样就可以得到确定的字输出顺序,从而可以不依赖训练码实现正确LVDS接收的字对齐。此方法不仅适合于FPGA与单独的LVDS发送器进行对接,也可用于FPGA与FPGA之间的数据传送,使用时FPGA的LVDS发送端送出低频的源同步时钟即可。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)