使用用CPLD和Flash实现FPGA的配置

时间:11-09

来源:互联网

点击:

- 2 具体设计

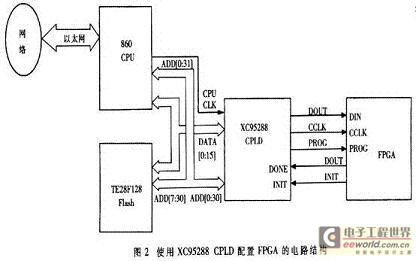

国家数字交换系统工程技术研究中心承担的国家863项目高性能IPv6核心路由器采用一片Intel E28F128J3A150 16位Flash作为BootFlash对PowerPC2860(MPC860)处理机进行加电配置下载更新的方案,其多余的存储空间完全可以存放下FPGA所需的配置文件。加电复位、系统启动后,由处理机与一片XilinxXC95288XL CPLD配合,控制FPGA配置文件从Flash下载到FPGA中,完成对FPGA的配置。860处理机支持网络功能,当配置文件需要更新时,可通过网络将新的配置文件发送到处理机,然后再由处理机更新系统中的Flash。采用XC95288CPLD配置FPGA的具体电路设计结构如图2所示。

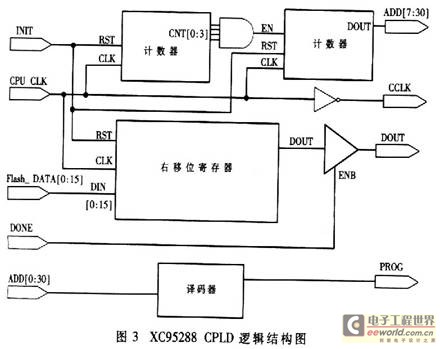

图2中,CPLD主要功能是把从Flash中读出的数据转换成串行输出,然后再将地址递增。CCLK(信号由CPU时钟产生。PROG信号则由CPU输出的地址数据经译码模块产生。XC95288C PLD逻辑结构如图3所示。

下面分别介绍各功能模块的具体实现:

(1)数据转换成串行输出功能模块:使用了一个右移寄存器。从16位Flash来的并行数据DIN[0:15]加载到移位寄存器后,依次从DOUT串行输出到FPGA中。

(2)地址递增功能模块:此功能由两个计数器完成。由于Flash是16位并行数据端口,因此第一个计数器功能是逢16进1,第二个计数器功能是Flash地址递增。当移位寄存器的16位数据都输出到FPGA中后,第一个计数器输出端口CNT[0:3]都为“1”,经过“与门”逻辑使得第二个计数器加l。Intel E28F128J3A150 Flash为16MB,共需要25根地址线。由于Flash是16位的,因此ADD[3l]不连接。所以第二个计数器和地址线ADD[7:30]相连.以完成Flash地址的递增。

(3)CCLK信号产生模块:CPU来的时钟信号将数据信号DOUT输出,经一个“非门”逻辑延迟半个周期后产生CCLK,CCLK再将DOUT上的数据送到FPGA中。这样将读写。DOUT数据的时刻叉开,避免了冲突。

(4)PROG信号产生模块:当需要下载FPGA程序时,由CPU产生一个地址信号ADD[O:30],经译码器译码产牛PROG控制信号。此地址由用户自行设定。

以上模块均采用VHDL语言描述。数据转换成串行输出功能模块是核心部分,它可实现并行数据串行输出。

本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。与传统的JTAG或PROM串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、适用于大容量FPGA下载的特点。采用此方法可以不用打开机箱即可随时更新FPGA配置程序,特别适用于需要不断更新的系统设计中,具有较为广阔的应用前景。

电子 自动化 EDA CPLD FPGA 集成电路 电路 VHDL Verilog Xilinx 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)