使用用CPLD和Flash实现FPGA的配置

时间:11-09

来源:互联网

点击:

电子设计自动化EDA(Electronic Design Automation)是指以计算机为工作平台,以EDA软件为开发环境,以硬件描述语言为设计语言,以可编程逻辑器件PLD为实验载体(包括CPLD、FPGA、EPLD等),以集成电路芯片为目标器件的电子产品自动化设计过程。该过程目前已广泛应用于电子电路与系统的设计和产品的开发中.逐渐取代了传统的手工硬件电路设计方式。设计的系统具有体积小、重量轻、功耗小、速度快、价格低、可靠性高、设计周期短等优点。一个功能完备的EDA设计软件加上一片普通功能的可编程逻辑芯片就可以构成以前需几百个集成电路才能构成的电子系统。

目前常用的可编程逻辑器件有CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)和FPGA(Field Programmable Gate Array,现场可编程门阵列)。常用的EDA软件包括VHDL、Verilog HDL、ABEL等硬件描述语言。其中,VHDL作为IEEE的工业标准硬件描述语言,受到众多EDA工具厂家的支持,在电子工程领域,已成为事实上的通用硬件描述语言。

Xilinx公司和Ahera公司的FPGA可编程部分的物理实现方式为RAM。它最大的优点是可以多次重复编翟,缺点是易失性。因此每次上电后,处理机都需要将用户设计的FPGA配置文件从外部存储器中下载到FPGA中。从外部存储器将FPGA配置文件下载更新的方式有以下三种:

(1)JTAG口下载方式

将配置文件放到一台主机中,主机通过专用线与单板上的JTAG口硬件相连接。在这种方式下每次下载都需要硬件操作,因此只适用于开发、调试阶段,设备在现场工作时就不能再使用这种方式。

(2)片外串行PROM下载方式

在每片FPGA周围放置一片或几片(由FPGA容量决定)串行PROM,在系统上电时,自动将FPGA配置文件从PROM下载到FPGA中。此方式也是xilinx、A1tera等公司重点介绍的方式,适用于比较稳定的系统。但随着FPGA芯片密度的增加,串行PROM已不能适应大容量、高密度的FPGA的配置。而大容量的并行PROM所要求的寻址方式又不能直接与FPGA接口。当系统中的FPGA配置文件需要升级更新时,必须将机箱打开,通过JTAG口首先将.PROM中的配置文件更新,然后再重新启动系统,将更新后的配置文件从PROM下载到FPGA中,这样才能完成一次FPGA配置文件的更新。

以上两种方案都存在必须进行硬件操作(将机箱打开,使用主机通过JTAG口)的缺点,在主机上必须安装专业软件才能完成FPGA配置文件的更新。

(3)处理机控制Flash下载方式

本文根据Xilinx、Altra公司手册及以前的工作经验,提出和完成了一种新的FPGA配置文件下载更新的方式。这种方式适用于支持网络通信的系统中。在每次系统启动时。由处理机从Flash中读出FPGA配置文件,再下载到FPGA中。即当需要升级更新FPGA配置文件时,通过网络将配置文件发送给处理机,由处理机更新系统中的Flash。当Flash内容更新后,再由处理机控制将配置文件自动下载到FPGA中。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。但由于Flash是并行数据线,需要通过一片CPLD将从Flash中读来的数据转换成串行数据输出到FPGA。

1 FPGA下载配置模式

FPGA配置文件的下载模式有五种:主串模式(masterserial)、从串模式(slave serial)、主并模式(master selectMAP)、从并模式(slave selectMAP)及JTAG模式。其中,JTAG模式在开发调试阶段使用。为了便于开发设计阶段的调试,本核心路由器设计将JTAG口直接做在信号处理板上。

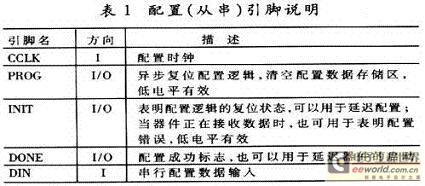

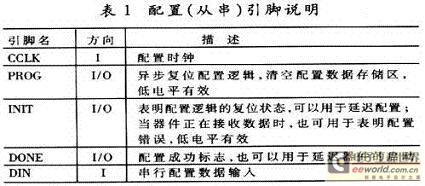

主、从模式的最大区别在于:主模式的下载同步时钟(CCLK)由FPGA提供;从模式的下载同步时钟(CCLK)由外部时钟源或者外部控制信号提供。主模式对下载时序的要求比从模式严格得多。因此从处理机易于控制下载过程的角度考虑,选择使用从串模式或从并模式较为合适。本设计采用从串模式进行FPGA配置。从串模式引脚说明如表l所示。

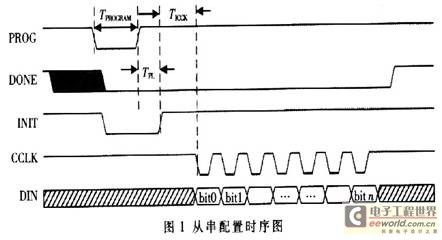

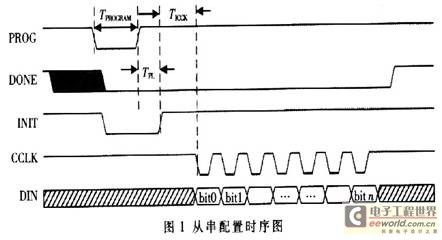

从串配置时序图如图l所示。TPROGRAM是配置逻辑的复位时间,对xilinx VIRTEXE和VIRTEX2系列,最小应大于300ns。TPL为复位延迟时问,表明配置逻辑复位的延续。对VIRTEXE系列来说,当复位信号PROG变为高电平时,INIT立即变为高电平,配置逻辑就可以接收配置数据流;而对于VIRTEX2系列,TPL最小有500ns的延迟。TICCK为配置时钟CCLK的输出延迟。

当PROG有效(对配置逻辑进行复位)时,FPGA将置低INIT和DONE;PROG变为高电平时,INIT将延迟一段时间用于表明复位状态的延续,继续置低INIT可以延迟配置的进行。当FPGA正在接收配置数据时,INIT变低,表明CRC校验错。当配置完所有的数据时,若配置正确,DONE将会变高。此后FPGA开始启动序列,继续置低DONE可以延迟启动的进行。

目前常用的可编程逻辑器件有CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)和FPGA(Field Programmable Gate Array,现场可编程门阵列)。常用的EDA软件包括VHDL、Verilog HDL、ABEL等硬件描述语言。其中,VHDL作为IEEE的工业标准硬件描述语言,受到众多EDA工具厂家的支持,在电子工程领域,已成为事实上的通用硬件描述语言。

Xilinx公司和Ahera公司的FPGA可编程部分的物理实现方式为RAM。它最大的优点是可以多次重复编翟,缺点是易失性。因此每次上电后,处理机都需要将用户设计的FPGA配置文件从外部存储器中下载到FPGA中。从外部存储器将FPGA配置文件下载更新的方式有以下三种:

(1)JTAG口下载方式

将配置文件放到一台主机中,主机通过专用线与单板上的JTAG口硬件相连接。在这种方式下每次下载都需要硬件操作,因此只适用于开发、调试阶段,设备在现场工作时就不能再使用这种方式。

(2)片外串行PROM下载方式

在每片FPGA周围放置一片或几片(由FPGA容量决定)串行PROM,在系统上电时,自动将FPGA配置文件从PROM下载到FPGA中。此方式也是xilinx、A1tera等公司重点介绍的方式,适用于比较稳定的系统。但随着FPGA芯片密度的增加,串行PROM已不能适应大容量、高密度的FPGA的配置。而大容量的并行PROM所要求的寻址方式又不能直接与FPGA接口。当系统中的FPGA配置文件需要升级更新时,必须将机箱打开,通过JTAG口首先将.PROM中的配置文件更新,然后再重新启动系统,将更新后的配置文件从PROM下载到FPGA中,这样才能完成一次FPGA配置文件的更新。

以上两种方案都存在必须进行硬件操作(将机箱打开,使用主机通过JTAG口)的缺点,在主机上必须安装专业软件才能完成FPGA配置文件的更新。

(3)处理机控制Flash下载方式

本文根据Xilinx、Altra公司手册及以前的工作经验,提出和完成了一种新的FPGA配置文件下载更新的方式。这种方式适用于支持网络通信的系统中。在每次系统启动时。由处理机从Flash中读出FPGA配置文件,再下载到FPGA中。即当需要升级更新FPGA配置文件时,通过网络将配置文件发送给处理机,由处理机更新系统中的Flash。当Flash内容更新后,再由处理机控制将配置文件自动下载到FPGA中。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。但由于Flash是并行数据线,需要通过一片CPLD将从Flash中读来的数据转换成串行数据输出到FPGA。

1 FPGA下载配置模式

FPGA配置文件的下载模式有五种:主串模式(masterserial)、从串模式(slave serial)、主并模式(master selectMAP)、从并模式(slave selectMAP)及JTAG模式。其中,JTAG模式在开发调试阶段使用。为了便于开发设计阶段的调试,本核心路由器设计将JTAG口直接做在信号处理板上。

主、从模式的最大区别在于:主模式的下载同步时钟(CCLK)由FPGA提供;从模式的下载同步时钟(CCLK)由外部时钟源或者外部控制信号提供。主模式对下载时序的要求比从模式严格得多。因此从处理机易于控制下载过程的角度考虑,选择使用从串模式或从并模式较为合适。本设计采用从串模式进行FPGA配置。从串模式引脚说明如表l所示。

从串配置时序图如图l所示。TPROGRAM是配置逻辑的复位时间,对xilinx VIRTEXE和VIRTEX2系列,最小应大于300ns。TPL为复位延迟时问,表明配置逻辑复位的延续。对VIRTEXE系列来说,当复位信号PROG变为高电平时,INIT立即变为高电平,配置逻辑就可以接收配置数据流;而对于VIRTEX2系列,TPL最小有500ns的延迟。TICCK为配置时钟CCLK的输出延迟。

当PROG有效(对配置逻辑进行复位)时,FPGA将置低INIT和DONE;PROG变为高电平时,INIT将延迟一段时间用于表明复位状态的延续,继续置低INIT可以延迟配置的进行。当FPGA正在接收配置数据时,INIT变低,表明CRC校验错。当配置完所有的数据时,若配置正确,DONE将会变高。此后FPGA开始启动序列,继续置低DONE可以延迟启动的进行。

电子 自动化 EDA CPLD FPGA 集成电路 电路 VHDL Verilog Xilinx 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)