增量型光电编码器抗抖动二倍频电路的设计

时间:11-09

来源:互联网

点击:

在某些工业自动控制领域、某些装备应用上,经常会遇到各种需要测量长度的场合,目前通常采用的是光电编码器。光电编码器根据其刻度方法及信号输出形式,可分为增量式、绝对式、混合式三种。它是一种集光、机、电为一体的传感器,具有精度高、响应快、性能稳定可靠等显著的优点,能够精确地检测角度、转速、位移等参数。它可以将位移等物理量转变为数字脉冲信号,通过计算脉冲的个数,实现精确的位移测量。然而由于工作环境等因素影响,增量型光电编码器输出信号中含有较多的抖动误码脉冲,将会引起误计数。本文分析误码脉冲产生的原因,设计一种有效的滤波电路。

1 增量型编码器的工作原理

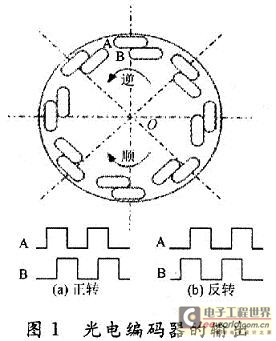

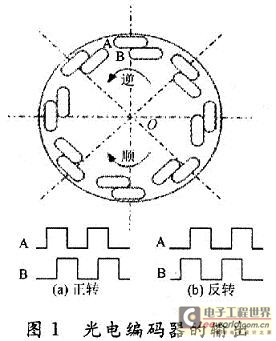

增量型编码器是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器,它由光栅盘和光电检测装置组成。光栅盘是在一定直径的圆板上等分地开通若干个长方形孔,见图1。由于光电码盘与电动机同轴,电动机旋转时,光栅盘与电动机同速旋转,经发光二极管等电子元件组成的检测装置检测输出若干脉冲信号,编码盘上涂有两道相差90°黑自相同的栅栏,分别称之为A道和B道。其输出脉冲也是相差90°。当编码器正向旋转时,A相比B相超前90°,当编码器反向旋转时,A相比B相滞后90°。正常情况下编码器的输出波形如图1所示。

2 误码脉冲产生的原因及其滤除方法

2.1 误码脉冲产生的原因

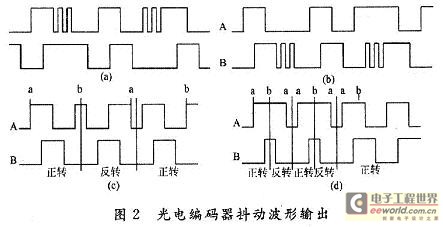

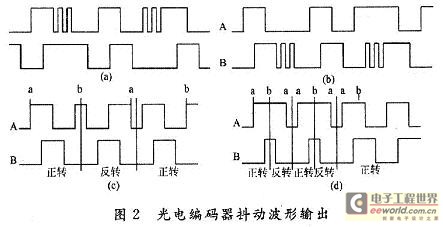

为了说明误码脉冲的存在性,将编码器码盘局部放大。图1中点0是编码器旋转轴的中心,圆角矩形代表码盘上A列和B列透光狭缝。假定编码器一相信号处于某种状态,而另一相信号处于高低电平跳变的交界状态,则编码器的误码脉冲如图2(a),图2(b)所示。由于电机的旋转或机械设备的振动,会使编码器输出脉冲抖动,从而引起误计数。它一方面表现为在透光窗口附近的抖动,引起的干扰脉冲,如图2(a)给出了A相脉冲信号在上升沿和下降沿发生抖动输出的时序波形,图2(b)给出了B相脉冲信号在上升沿和下降沿发生抖动输出的时序波形;另一方面表现为在编码器的某点附近前后振动,引起干扰脉冲。如图2(c),图2(d)给出了信号在编码器b点前后抖动的时序波形。编码器从a点正转到b点,然后编码器反转到a点,又正转到b点,两个b点之间的脉冲数为干扰脉冲。

2.2 误码脉冲的滤除

2.2.1 滤除编码器抖动的原理

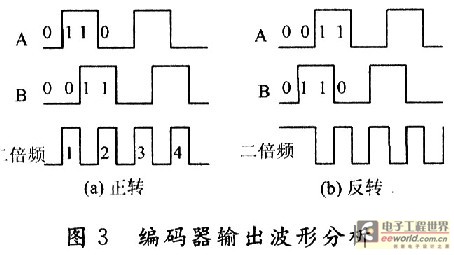

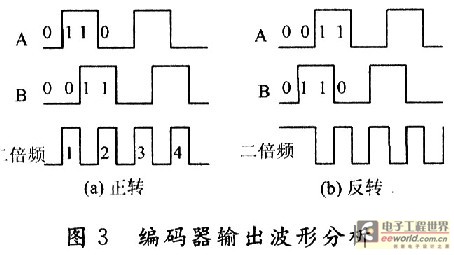

采用二倍频技术滤除抖动脉冲。所谓二倍频技术即对A相或者B相每个脉冲的上升沿和下降沿分别计数。光电编码器经过二倍频后正常输出波形如图3所示,A相脉冲O→1跳变时,B为O,则编码器正转;B为1,则编码器反转。A相脉冲1→O跳变时,B为1,则编码器正转;B为0,则编码器反转。编码器正常输出波形时,A、B两相交替跳变,如果A相发生跳变后,B相没有发生跳变A相又发生跳变,此时认为是干扰脉冲,反之同样视为干扰脉冲。

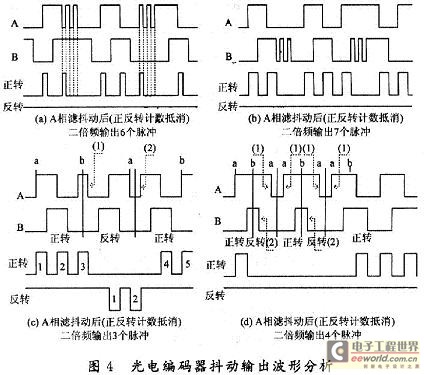

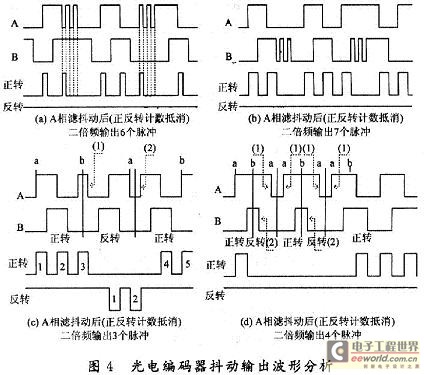

分析图4,对A相的跳变沿进行二倍频计数,B相的高低电平用来判断编码器的正反转。B相边沿的抖动脉冲对二倍频计数没有影响,如图4(b)所示。分析图4(a),A相边缘的抖动认为是干扰脉冲被滤除掉。图4(c),图4(d)中的a,b标记的位置是编码器物理地址,如图4(d)标记的a,b表示编码器在此处反复振动。图4(c)、图4(d)(1)、(2)标记处跳变沿视为抖动脉冲,应滤除,A相的正转脉冲数据数和反转脉冲数据数相减后就是A相实际二倍频后的脉冲数据。

2.2.2 FPGA滤除编码器抖动及仿真结果

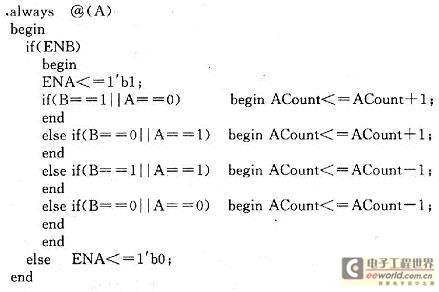

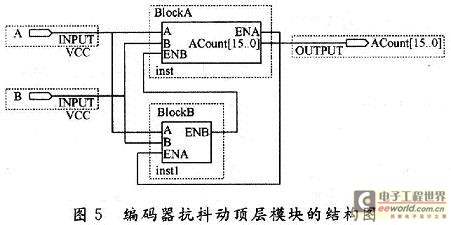

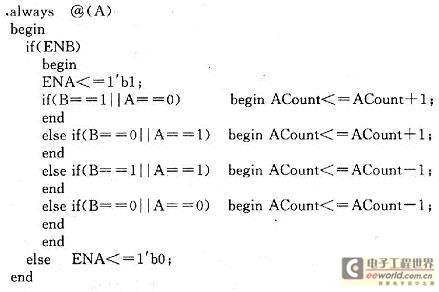

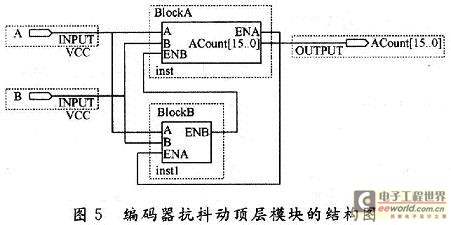

根据以上分析,本文采用FPGA滤除增量型光电编码器输出抖动脉冲。编译环境采用QuartusⅡ8.O。在FPGA中使用图形和语言结合的方法设计逻辑模块。内部的逻辑子模块采用Verilog语言来实现。顶层模块的结构图如图5所示。A和B输入引脚连接增量型编码器A相和B相信号。Acount为16位的数据寄存器,输出当前编码器的位置。顶层设计中包含两个模块,一个是根据编码器的B相跳变沿记录来滤除编码器A相抖动脉冲的BlockA模块,该模块根据滤除后的A相脉冲数据个数并记录脉冲数据。Verilog的主要程序如下:

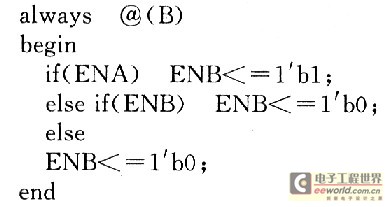

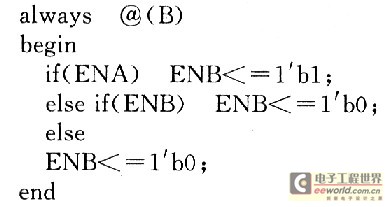

另一个模块BlockB主要完成的功能是滤除编码器B相的抖动脉冲。根据分析滤除编码器抖动的原理,ENA引脚为BlockA模块的输出引脚,当A相输入引脚有跳变时ENA为1,A相引脚有连续的跳变或者接下来B相有跳变时ENA为0。ENB为编码器B相跳变使能引脚,当ENA为1时如果B相有跳变ENB为1,当ENA为1时如果B相有连续跳变ENB为0。主要程序如下:

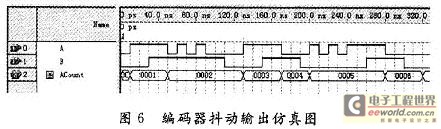

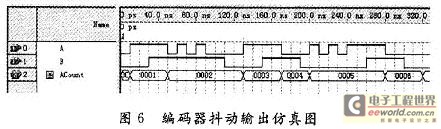

以图4(a)的编码器抖动输出仿真为例,仿真效果如图6所示。从图中分析,A相输出7个脉冲,应该输出3个脉冲,二倍频后是14个脉冲,应该输出6个脉冲,经过滤除后脉冲计数器数为6个。A相的抖动脉冲得到有效的滤除。

1 增量型编码器的工作原理

增量型编码器是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器,它由光栅盘和光电检测装置组成。光栅盘是在一定直径的圆板上等分地开通若干个长方形孔,见图1。由于光电码盘与电动机同轴,电动机旋转时,光栅盘与电动机同速旋转,经发光二极管等电子元件组成的检测装置检测输出若干脉冲信号,编码盘上涂有两道相差90°黑自相同的栅栏,分别称之为A道和B道。其输出脉冲也是相差90°。当编码器正向旋转时,A相比B相超前90°,当编码器反向旋转时,A相比B相滞后90°。正常情况下编码器的输出波形如图1所示。

2 误码脉冲产生的原因及其滤除方法

2.1 误码脉冲产生的原因

为了说明误码脉冲的存在性,将编码器码盘局部放大。图1中点0是编码器旋转轴的中心,圆角矩形代表码盘上A列和B列透光狭缝。假定编码器一相信号处于某种状态,而另一相信号处于高低电平跳变的交界状态,则编码器的误码脉冲如图2(a),图2(b)所示。由于电机的旋转或机械设备的振动,会使编码器输出脉冲抖动,从而引起误计数。它一方面表现为在透光窗口附近的抖动,引起的干扰脉冲,如图2(a)给出了A相脉冲信号在上升沿和下降沿发生抖动输出的时序波形,图2(b)给出了B相脉冲信号在上升沿和下降沿发生抖动输出的时序波形;另一方面表现为在编码器的某点附近前后振动,引起干扰脉冲。如图2(c),图2(d)给出了信号在编码器b点前后抖动的时序波形。编码器从a点正转到b点,然后编码器反转到a点,又正转到b点,两个b点之间的脉冲数为干扰脉冲。

2.2 误码脉冲的滤除

2.2.1 滤除编码器抖动的原理

采用二倍频技术滤除抖动脉冲。所谓二倍频技术即对A相或者B相每个脉冲的上升沿和下降沿分别计数。光电编码器经过二倍频后正常输出波形如图3所示,A相脉冲O→1跳变时,B为O,则编码器正转;B为1,则编码器反转。A相脉冲1→O跳变时,B为1,则编码器正转;B为0,则编码器反转。编码器正常输出波形时,A、B两相交替跳变,如果A相发生跳变后,B相没有发生跳变A相又发生跳变,此时认为是干扰脉冲,反之同样视为干扰脉冲。

分析图4,对A相的跳变沿进行二倍频计数,B相的高低电平用来判断编码器的正反转。B相边沿的抖动脉冲对二倍频计数没有影响,如图4(b)所示。分析图4(a),A相边缘的抖动认为是干扰脉冲被滤除掉。图4(c),图4(d)中的a,b标记的位置是编码器物理地址,如图4(d)标记的a,b表示编码器在此处反复振动。图4(c)、图4(d)(1)、(2)标记处跳变沿视为抖动脉冲,应滤除,A相的正转脉冲数据数和反转脉冲数据数相减后就是A相实际二倍频后的脉冲数据。

2.2.2 FPGA滤除编码器抖动及仿真结果

根据以上分析,本文采用FPGA滤除增量型光电编码器输出抖动脉冲。编译环境采用QuartusⅡ8.O。在FPGA中使用图形和语言结合的方法设计逻辑模块。内部的逻辑子模块采用Verilog语言来实现。顶层模块的结构图如图5所示。A和B输入引脚连接增量型编码器A相和B相信号。Acount为16位的数据寄存器,输出当前编码器的位置。顶层设计中包含两个模块,一个是根据编码器的B相跳变沿记录来滤除编码器A相抖动脉冲的BlockA模块,该模块根据滤除后的A相脉冲数据个数并记录脉冲数据。Verilog的主要程序如下:

另一个模块BlockB主要完成的功能是滤除编码器B相的抖动脉冲。根据分析滤除编码器抖动的原理,ENA引脚为BlockA模块的输出引脚,当A相输入引脚有跳变时ENA为1,A相引脚有连续的跳变或者接下来B相有跳变时ENA为0。ENB为编码器B相跳变使能引脚,当ENA为1时如果B相有跳变ENB为1,当ENA为1时如果B相有连续跳变ENB为0。主要程序如下:

以图4(a)的编码器抖动输出仿真为例,仿真效果如图6所示。从图中分析,A相输出7个脉冲,应该输出3个脉冲,二倍频后是14个脉冲,应该输出6个脉冲,经过滤除后脉冲计数器数为6个。A相的抖动脉冲得到有效的滤除。

编码器 传感器 电路 电动机 二极管 电子 FPGA 仿真 Quartus Verilog 相关文章:

- 基于CPLD的开放式四轴运动控制器的设计(06-23)

- WCDMA速率适配算法的FPGA实现(07-11)

- 基于 FPGA 的 MPEG-4 编解码器(07-18)

- CPLD与绝对式编码器在高精度高速伺服单元中的应用(07-28)

- CPLD在射频卡读写器中的应用(08-02)

- 一种基于CPLD的曼彻斯特编解码器设计(08-06)