基于FPGA的高速时钟数据恢复电路的实现

时间:11-08

来源:互联网

点击:

2.3.2 时钟切换

采用时钟切换实现该相位调整,首要问题就是必须消除时钟切换时产生的毛刺,因此所有子电路都采用恢复出来的时钟信号作为其工作时钟,这样所有的时钟切换情况都可用图5表示。假定此时的工作时钟为clk_l,只要能够保证时钟切换避开上面的阴影区域,而是处在上图中的红色区域,则无论是时钟向前还是向后切换,都不会出现毛刺。以工作频率为200MHz计算,每段红色区域大约为1.6ns,而Altera中的LE单元延迟大约为0.23ns,所以采用buffer弥补延迟完全可以使时钟切换发生在合适的位置。

2.3.3 时钟相位偏移的补偿

该电路结构的另一关键是必须保证不同相位时钟信号经过时钟判断调整模块后,它们之间的相位关系不会因延迟的不同而失效而必须仍然成立,否则就会导致相位调整过大或过小,电路会因此变得不稳定。电路延迟由门延迟和连线延迟组成。对于连线延迟在AlteraCyclone II中只要两个LE之间的连线类型相同,延迟也就相同,而每个LAB中有16个LE也有16个LOCAL LINE布线资源,因此同一个LAB 中LE之间的互连线延迟都是相同的。对于门延迟,在Cyclone II中每个LE有A、B、C、D四个输入端,各端口延迟不同。首先通过在某些路径上插入buffer,使得所有时钟信号经过的LE的数目相同。然后再在3个时钟信号中各插入一个buffer,再根据最终的布线情况,调整这3个buffer的端口连接,就可以使得各时钟信号经过的门延迟基本相同。除了上述两种方法,在应用中使用了Quartus II的Logiclock功能,按照设计的需要将同一功能模块的逻辑放在相同的LAB中,这样可以使连线延迟对电路的影响降到最小。同时利用该功能也可以直接将调整好的时钟恢复电路应用于整个通信系统中,使得其他电路的布局布线不会对该电路产生影响。

2.4 数据恢复

由于时钟数据恢复电路的目的就是得到能够正确采样输入数据的时钟信号。为了保证恢复出的时钟和输入数据的相位关系在整个芯片内都能够成立,在系统应用中输入信号也走全局时钟网络。经过这样处理后,只要在需要恢复数据的地方加一个D触发器即可得到正确的数据信号。

3 环路仿真结果及讨论

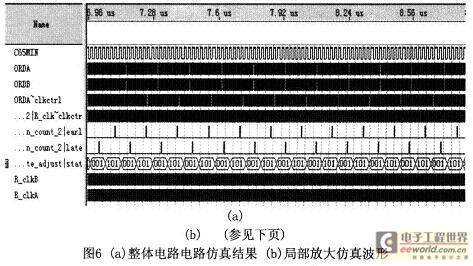

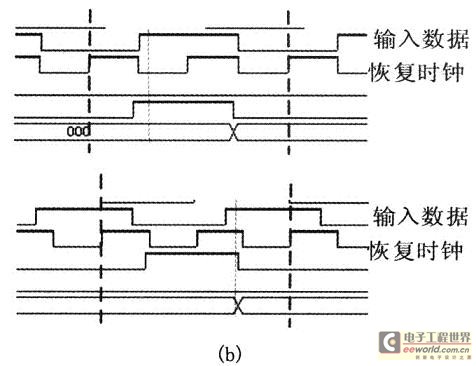

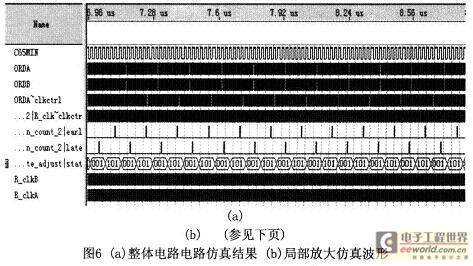

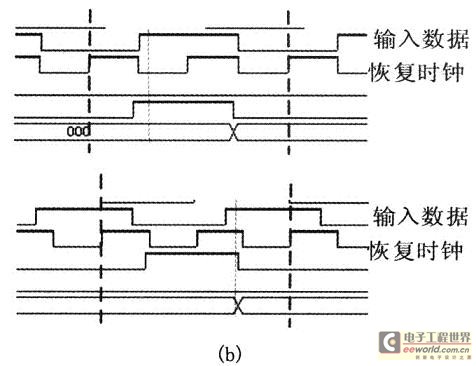

采用EP2C5T144C6器件的环路的仿真结果如图6所示,其中工作频率为204.8MHz。由于整个电路用的是经过全局时钟控制模块后的时钟和输入数据,所以在图6中给出的是这两个信号时序关系:ORDA"clkctrl和R_clk"clkctrl。由图(a)及局部放大图(b)可以看出,电路稳定时钟信号在输入数据的中间位置左右摆动,可以正确采样输入数据。

本文提出的电路结构不需要高频时钟信号,因此只要相位调整过程中时钟信号的脉冲宽度大于器件要求的最小值,且满足整个电路满足建立保持时间就可以正常工作。因此最小的时钟周期T=max(3*Tmin,Tper),其中Tmin是所用器件时钟信号脉冲宽度的最小值,Tper是满足建立保持时间的最小时钟周期。例如EP2C35F672C6芯片工作时钟高电平脉冲最小值为1ns,采用该芯片电路的工作频率可以达到300MHz,这个工作频率已经通过了Altera DE2板的硬件验证。如果采用更快的器件如Cyclone III EP3C10T144C7,时钟脉冲宽度最小值0.625ns,经过仿真验证其工作频率可以达到400MHz。在时钟调整模块后加一个简单的二分频电路,就可以实现12个时钟相位的调整精度,根据不同器件的性能很容易进行扩展,达到所需要的设计要求。

4 结论

本文利用时钟切换的方法,在低端AlteraEP2C5T144C6上实现了204.8MHZ的时钟数据恢复电路,并通过了硬件验证。通过理论分析给出了决定该电路工作频率的主要因素,同时对该电路稍加改动就可以实现更高精度的时钟数据恢复电路,具有很好的扩展性,为利用中低端FPGA实现高速通信系统提供了一种可参考的解决方案。

采用时钟切换实现该相位调整,首要问题就是必须消除时钟切换时产生的毛刺,因此所有子电路都采用恢复出来的时钟信号作为其工作时钟,这样所有的时钟切换情况都可用图5表示。假定此时的工作时钟为clk_l,只要能够保证时钟切换避开上面的阴影区域,而是处在上图中的红色区域,则无论是时钟向前还是向后切换,都不会出现毛刺。以工作频率为200MHz计算,每段红色区域大约为1.6ns,而Altera中的LE单元延迟大约为0.23ns,所以采用buffer弥补延迟完全可以使时钟切换发生在合适的位置。

2.3.3 时钟相位偏移的补偿

该电路结构的另一关键是必须保证不同相位时钟信号经过时钟判断调整模块后,它们之间的相位关系不会因延迟的不同而失效而必须仍然成立,否则就会导致相位调整过大或过小,电路会因此变得不稳定。电路延迟由门延迟和连线延迟组成。对于连线延迟在AlteraCyclone II中只要两个LE之间的连线类型相同,延迟也就相同,而每个LAB中有16个LE也有16个LOCAL LINE布线资源,因此同一个LAB 中LE之间的互连线延迟都是相同的。对于门延迟,在Cyclone II中每个LE有A、B、C、D四个输入端,各端口延迟不同。首先通过在某些路径上插入buffer,使得所有时钟信号经过的LE的数目相同。然后再在3个时钟信号中各插入一个buffer,再根据最终的布线情况,调整这3个buffer的端口连接,就可以使得各时钟信号经过的门延迟基本相同。除了上述两种方法,在应用中使用了Quartus II的Logiclock功能,按照设计的需要将同一功能模块的逻辑放在相同的LAB中,这样可以使连线延迟对电路的影响降到最小。同时利用该功能也可以直接将调整好的时钟恢复电路应用于整个通信系统中,使得其他电路的布局布线不会对该电路产生影响。

2.4 数据恢复

由于时钟数据恢复电路的目的就是得到能够正确采样输入数据的时钟信号。为了保证恢复出的时钟和输入数据的相位关系在整个芯片内都能够成立,在系统应用中输入信号也走全局时钟网络。经过这样处理后,只要在需要恢复数据的地方加一个D触发器即可得到正确的数据信号。

3 环路仿真结果及讨论

采用EP2C5T144C6器件的环路的仿真结果如图6所示,其中工作频率为204.8MHz。由于整个电路用的是经过全局时钟控制模块后的时钟和输入数据,所以在图6中给出的是这两个信号时序关系:ORDA"clkctrl和R_clk"clkctrl。由图(a)及局部放大图(b)可以看出,电路稳定时钟信号在输入数据的中间位置左右摆动,可以正确采样输入数据。

本文提出的电路结构不需要高频时钟信号,因此只要相位调整过程中时钟信号的脉冲宽度大于器件要求的最小值,且满足整个电路满足建立保持时间就可以正常工作。因此最小的时钟周期T=max(3*Tmin,Tper),其中Tmin是所用器件时钟信号脉冲宽度的最小值,Tper是满足建立保持时间的最小时钟周期。例如EP2C35F672C6芯片工作时钟高电平脉冲最小值为1ns,采用该芯片电路的工作频率可以达到300MHz,这个工作频率已经通过了Altera DE2板的硬件验证。如果采用更快的器件如Cyclone III EP3C10T144C7,时钟脉冲宽度最小值0.625ns,经过仿真验证其工作频率可以达到400MHz。在时钟调整模块后加一个简单的二分频电路,就可以实现12个时钟相位的调整精度,根据不同器件的性能很容易进行扩展,达到所需要的设计要求。

4 结论

本文利用时钟切换的方法,在低端AlteraEP2C5T144C6上实现了204.8MHZ的时钟数据恢复电路,并通过了硬件验证。通过理论分析给出了决定该电路工作频率的主要因素,同时对该电路稍加改动就可以实现更高精度的时钟数据恢复电路,具有很好的扩展性,为利用中低端FPGA实现高速通信系统提供了一种可参考的解决方案。

电路 收发器 FPGA PCB Altera Quartus 仿真 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)