基于FPGA的高速时钟数据恢复电路的实现

时间:11-08

来源:互联网

点击:

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载的通信速率已经可以达到GHz,从而使得接收端的接收速率成为限制通信速率的主要瓶颈。因此高速时钟数据恢复电路的研究是目前通信领域的研究热点。目前时钟数据恢复电路主要是模拟IC和数字IC,其频率已经可以达到几十GHz。而由于FPGA器件的可编程性、低成本、短的设计周期以及越来越大的容量和速度,在数字领域的应用逐渐有替代数字IC的趋势,已经广泛作为数字系统的控制核心。但利用中低端FPGA还没有可以达到100MHz以上的时钟数据恢复电路。由于上面的原因,许多利用FPGA实现的高速通信系统中必须使用额外的专用时钟数据恢复IC,这样不仅增加了成本,而且裸露在外的高速PCB布线使还会带来串扰、信号完整性等非常严重的问题。如果可以在中低端FPGA上实现高速时钟数据恢复电路,则可降低成本且提高整个电路系统的性能。

目前利用FPGA实现时钟恢复电路的方法,基本都是首先利用FPGA内部的锁相环产生N*f的高频时钟,然后再根据输入信号控制对高速时钟的分频,从而产生与输入信号同步的时钟信号,其中N决定了恢复时钟信号的相位精度,通常N等于8。因此如果输入信号的频率为100MHz,则系统的工作频率就必须达到800MHz,对于中低端FPGA,如此高的工作频率显然无法承受。虽然高端FPGA可以达到GHz的工作频率,但其高昂的价格不适合用于普通用户。而其它基于中低端FPGA实现高速时钟恢复电路的方法,要么需要外部VCO模块,要么只能恢复数据而无法得到同步的时钟信号。针对这种情况,本文提出了一种利用Altera FPGA中的锁相环及Logiclock等技术,实现高速时钟恢复电路的方法。电路是在Altera的EP2C5T144C6芯片上实现的,用于数字光端机的接收端从100路2.048MHz压缩视频码流合成的串行码流中正确提取100路视频码流,其工作频率为204.8MHz,通过硬件验证电路可以正确工作。

1 时钟恢复电路原理及环路结构

时钟恢复电路的目的是从输入的数据流中,提取出与其同步的时钟信号。时钟信号不可能凭空产生,因此该电路本身必须有一个时钟信号产生机制,除此之外还必须有一个判断控制机制一能够判断并且调整该时钟信号与输入数据之间的相位关系,使其同步。

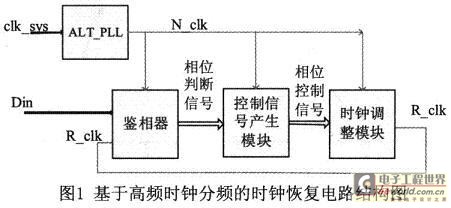

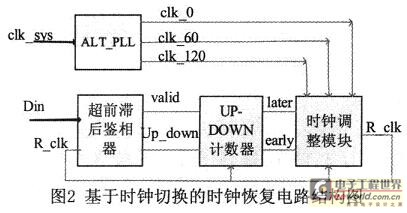

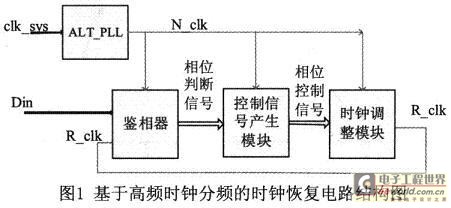

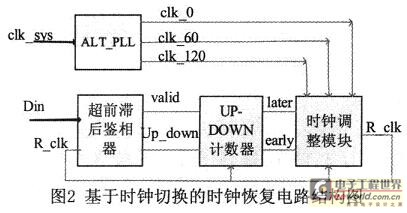

传统的基于FPGA的时钟恢复电路的结构如图1所示。如前所述,这种结构的电路用中低端FPGA,工作频率不可能达到100MHz以上。本文采用的方法是利用锁相环产生不同相位的时钟信号,然后再根据控制信号控制输出时钟在这些时钟之间进行切换,从而使时钟与输入数据同步。具体结构如图2所示。下面详细介绍各个模块的工作原理及电路实现。

2 模块电路设计

电路由三个模块构成,鉴相器模块和计数器模块通过判断时钟信号和输入信号的相位关系,产生相位调整的控制信号,时钟调整模块根据送来的控制信号对输出时钟进行相位调整。

2.1 超前滞后鉴相器

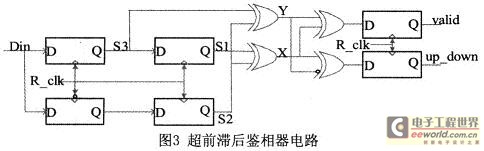

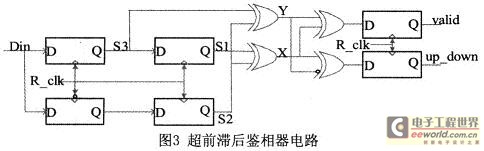

鉴相器使用可以识别输入信号连0和连1的超前滞后鉴相器,具体电路如图3所示。利用四个D触发器对输入信号Din采样产生s1、s2、s3三个信号,如果s2=s3≠s1,则表示时钟超前,up-down为高电平;如果s1=s2≠s3,则表示时钟滞后,up-down为低电平;当输入信号连0或连1时s1=s2=s3,valid为低电平,此时up-down无效。这两个信号都必须用时钟信号进行同步产生,否则电路可能由于s1、s2、s3的延迟差而进入一种死锁状态。这种鉴相器只有超前或滞后两种状态,如果直接将其输出用作控制时钟相位的调整,则时钟切换会过于频繁,而且输入信号中的毛刺会引起误操作。所以将其输出信号送给up-down计数模块,进行一段时间的积累后,再产生用于控制时钟相位的信号。

2.2 up-down计数器模块

计数器模块的功能是在鉴相器送来的信号控制下进行计数,产生相位调整的控制信号。计数器的初始值为M,当输入信号valid为高电平时,判断up-down信号。如果该信号为1,则计数器加计数,否则减计数。当计数器的值为2M时,early产生高电平脉冲;当为0时,later产生高电平脉冲。

2.3 时钟产生调整模块

2.3.1 电路结构

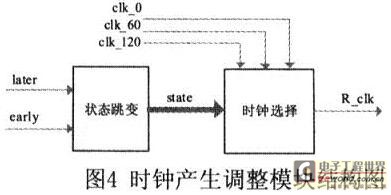

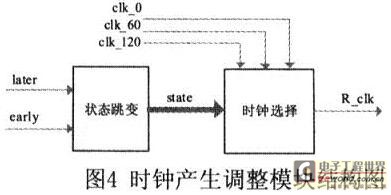

时钟产生调整模块的主要功能是产生和输入信号频率相同的时钟信号,并根据相位判断模块发送过来的控制信号,不断地调整输出时钟相位,使得输出时钟的上升沿维持在输入信号中间位置,其结构如图4所示。不同相位的同频时钟是利用EP2C5T144C6 中的锁相环产生的,由于课题项目的需要,1个片子内部必须含有2个时钟恢复电路,受到全局时钟数目的限制,采用6个时钟信号进行切换。在该模块电路设计设置6个状态,每一状态对应某一相位的时钟信号。当检测到early信号为高电平时,状态就跳变到比当前时钟信号相位提前1个相位的状态上(若相位超前则再继续超前),而当later信号为高电平时跳变到比当前时钟信号滞后1个相位的状态上去(相位滞后则继续滞后),然后再根据当前的状态选择相应的时钟信号,作为当前工作时钟即输出时钟信号Rclk。

目前利用FPGA实现时钟恢复电路的方法,基本都是首先利用FPGA内部的锁相环产生N*f的高频时钟,然后再根据输入信号控制对高速时钟的分频,从而产生与输入信号同步的时钟信号,其中N决定了恢复时钟信号的相位精度,通常N等于8。因此如果输入信号的频率为100MHz,则系统的工作频率就必须达到800MHz,对于中低端FPGA,如此高的工作频率显然无法承受。虽然高端FPGA可以达到GHz的工作频率,但其高昂的价格不适合用于普通用户。而其它基于中低端FPGA实现高速时钟恢复电路的方法,要么需要外部VCO模块,要么只能恢复数据而无法得到同步的时钟信号。针对这种情况,本文提出了一种利用Altera FPGA中的锁相环及Logiclock等技术,实现高速时钟恢复电路的方法。电路是在Altera的EP2C5T144C6芯片上实现的,用于数字光端机的接收端从100路2.048MHz压缩视频码流合成的串行码流中正确提取100路视频码流,其工作频率为204.8MHz,通过硬件验证电路可以正确工作。

1 时钟恢复电路原理及环路结构

时钟恢复电路的目的是从输入的数据流中,提取出与其同步的时钟信号。时钟信号不可能凭空产生,因此该电路本身必须有一个时钟信号产生机制,除此之外还必须有一个判断控制机制一能够判断并且调整该时钟信号与输入数据之间的相位关系,使其同步。

传统的基于FPGA的时钟恢复电路的结构如图1所示。如前所述,这种结构的电路用中低端FPGA,工作频率不可能达到100MHz以上。本文采用的方法是利用锁相环产生不同相位的时钟信号,然后再根据控制信号控制输出时钟在这些时钟之间进行切换,从而使时钟与输入数据同步。具体结构如图2所示。下面详细介绍各个模块的工作原理及电路实现。

2 模块电路设计

电路由三个模块构成,鉴相器模块和计数器模块通过判断时钟信号和输入信号的相位关系,产生相位调整的控制信号,时钟调整模块根据送来的控制信号对输出时钟进行相位调整。

2.1 超前滞后鉴相器

鉴相器使用可以识别输入信号连0和连1的超前滞后鉴相器,具体电路如图3所示。利用四个D触发器对输入信号Din采样产生s1、s2、s3三个信号,如果s2=s3≠s1,则表示时钟超前,up-down为高电平;如果s1=s2≠s3,则表示时钟滞后,up-down为低电平;当输入信号连0或连1时s1=s2=s3,valid为低电平,此时up-down无效。这两个信号都必须用时钟信号进行同步产生,否则电路可能由于s1、s2、s3的延迟差而进入一种死锁状态。这种鉴相器只有超前或滞后两种状态,如果直接将其输出用作控制时钟相位的调整,则时钟切换会过于频繁,而且输入信号中的毛刺会引起误操作。所以将其输出信号送给up-down计数模块,进行一段时间的积累后,再产生用于控制时钟相位的信号。

2.2 up-down计数器模块

计数器模块的功能是在鉴相器送来的信号控制下进行计数,产生相位调整的控制信号。计数器的初始值为M,当输入信号valid为高电平时,判断up-down信号。如果该信号为1,则计数器加计数,否则减计数。当计数器的值为2M时,early产生高电平脉冲;当为0时,later产生高电平脉冲。

2.3 时钟产生调整模块

2.3.1 电路结构

时钟产生调整模块的主要功能是产生和输入信号频率相同的时钟信号,并根据相位判断模块发送过来的控制信号,不断地调整输出时钟相位,使得输出时钟的上升沿维持在输入信号中间位置,其结构如图4所示。不同相位的同频时钟是利用EP2C5T144C6 中的锁相环产生的,由于课题项目的需要,1个片子内部必须含有2个时钟恢复电路,受到全局时钟数目的限制,采用6个时钟信号进行切换。在该模块电路设计设置6个状态,每一状态对应某一相位的时钟信号。当检测到early信号为高电平时,状态就跳变到比当前时钟信号相位提前1个相位的状态上(若相位超前则再继续超前),而当later信号为高电平时跳变到比当前时钟信号滞后1个相位的状态上去(相位滞后则继续滞后),然后再根据当前的状态选择相应的时钟信号,作为当前工作时钟即输出时钟信号Rclk。

电路 收发器 FPGA PCB Altera Quartus 仿真 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)