VHDL上机手册

时间:09-26

来源:互联网

点击:

12 布局布线后的仿真( Simulate Post-Place&Route VHDL Model)

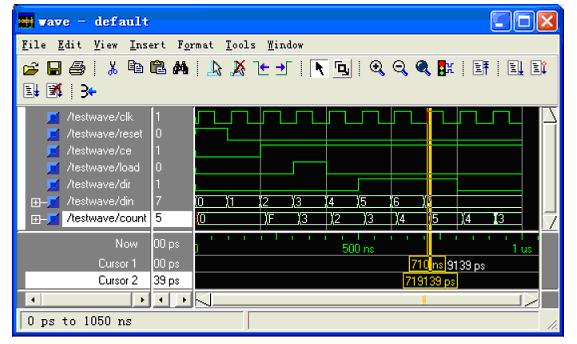

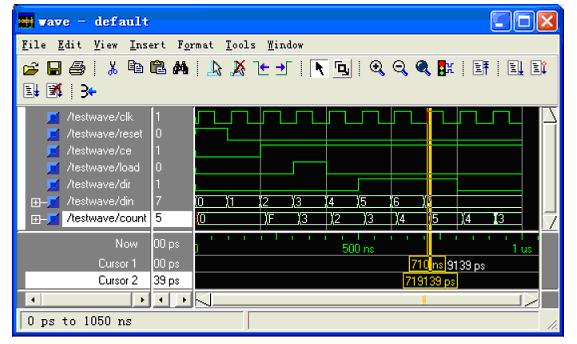

布局布线后仿真利用了从布局布线中提取出的一些信息,其中包括了目标器件及互连线的时延、电阻、电容等信息。具体仿真步骤与行为仿真相同。只是在第三步,双击Simulate Post-Place&Route VHDL Model 就可以了。仿真波形图如图19 所示。可以看到,时钟上升沿和计数值改变的时刻之间相差8296ps(图中两根竖线之间的间距),说明了器件的延时加上互连线延时为6794ps。

图19 ModelSim 布局布线后仿真结果

布局布线后仿真利用了从布局布线中提取出的一些信息,其中包括了目标器件及互连线的时延、电阻、电容等信息。具体仿真步骤与行为仿真相同。只是在第三步,双击Simulate Post-Place&Route VHDL Model 就可以了。仿真波形图如图19 所示。可以看到,时钟上升沿和计数值改变的时刻之间相差8296ps(图中两根竖线之间的间距),说明了器件的延时加上互连线延时为6794ps。

图19 ModelSim 布局布线后仿真结果

ModelSim VHDL 仿真 Xilinx PCB FPGA Verilog CPLD 电容 电阻 EDA 相关文章:

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA的微处理器内核设计与实现(06-21)

- 基于PLD的纳秒级脉冲发生器(07-24)

- FPGA的八位RISC CPU的设计(07-29)

- 基于FPGA的以太网控制器设计(07-28)

- 基于FPGA的八位RISC CPU的设计(08-02)