VHDL上机手册

时间:09-26

来源:互联网

点击:

3 创建一个VHDL源文件框架

在本小节我们向刚刚创建的工程中添加设计文件来实现要求的功能。按照以下步骤建立一个计数器的VHDL 文件描述。注意这里仅仅新建一个有框架的文件,下一小节将向该文件中添加具体代码。

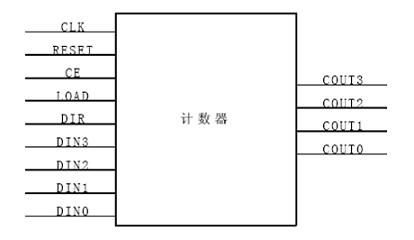

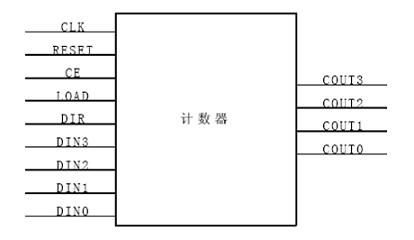

在这里我们以一个具有复位(reset)、使能(ce)、置数(load)、计数方向控制(dir)功能的计数器为基础进行设计。其方块图如图5 所示。其中CLK 为输入计数时钟信号,系统在该信号的驱动下开始工作;RESET 为复位信号,在上升沿处,输入复位为全零;CE 为使能信号,为1 时计数正常进行,为0 时停止计数;LOAD 为置数信号,当在时钟上升沿该信号为1 时,将DIN0~DIN3 分别置给COUT0~COUT3。DIR 为计数方向控制,为1 时递增计数,为0 时递减计数。这些功能描述只是我们的设计目标,或称为设计需求,我们在设计一个系统时,第一步就是要明确我们的设计要求。

图5 计数器方块图

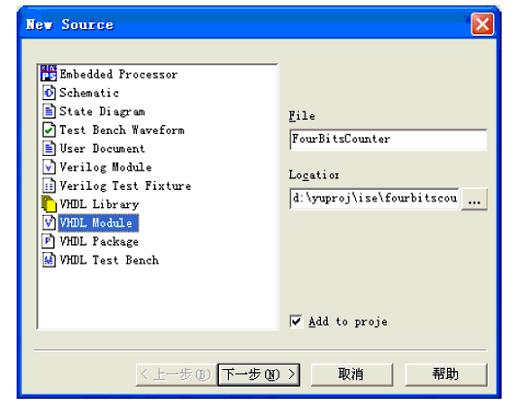

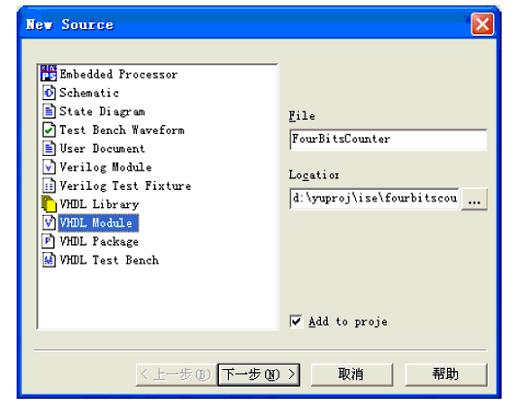

Step1. 选择Project->New Source;(或在Sources in Project 窗口中单击鼠标右键选择“New Source…”)出现如图6 所示的窗口;

图6 源程序的类型选择

Step2. 选择VHDL Module(VHDL 模块)作为新建源文件的类型;

Step3. 在文件名中键入“FourBitsCounter”;

Step4. 单击“下一步”;

Step5. 单击“下一步”;

Step6. 单击“完成”,完成这个新源程序的创建。新源程序文件FourBitsCounter.vhd 将会显示在HDL 编辑窗口中,它包括Library,Use,Entity,Architecture 等语句。

4 利用计数器模板向导生成设计

设计文件建立之后,我们就可以向其中填写代码了。我们可以直接书写HDL 代码,也可以利用ISE 的语言模板(ISE Language Template)工具来辅助我们书写HDL 代码。在这里我们使用语言模板,选择其中的计数器描述来完成本源程序的设计。

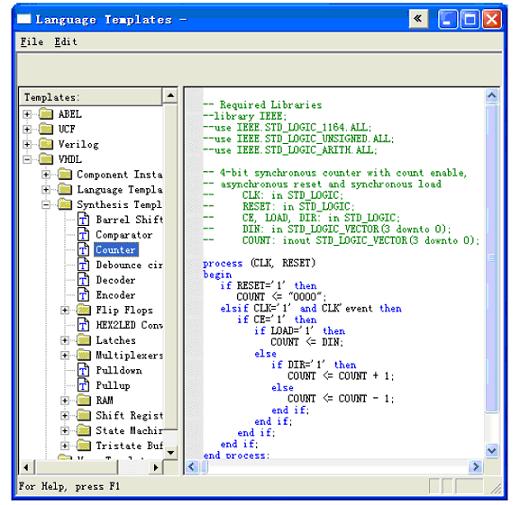

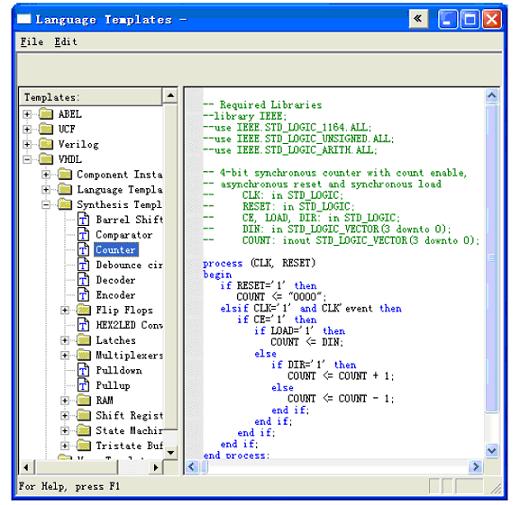

Step1. 选择Edit->Language Templates 打开语言模板,或者通过单击按钮 来打开语言模板,如图7 所示;

图7 计数器语言模板

Step2. 在Language Templates 中通过单击“+”来展开VHDL 下的综合模板(Synthesis Templates);

Step3. 从VHDL 综合模板中选择计数器模板(Counter Template),并把它粘贴到源程序counter.vhd 的begin 和end 之间。(或在Counter Template 上单击右键选择“Use incounter.vhd”,建议直接复制过去);

Step4. 关闭Language Templates 窗口;

Step5. 将带有注释符号“--”的计数器端口定义语句剪切并粘贴到计数器的实体(entity)描述中。这些语句如下所列:

-- CLK: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- CE, LOAD, DIR: in STD_LOGIC;

-- DIN: in STD_LOGIC_VECTOR(3 downto 0);

-- COUNT: inout STD_LOGIC_VECTOR(3 downto 0);

Step6. 去掉上述语句中的注释符号;

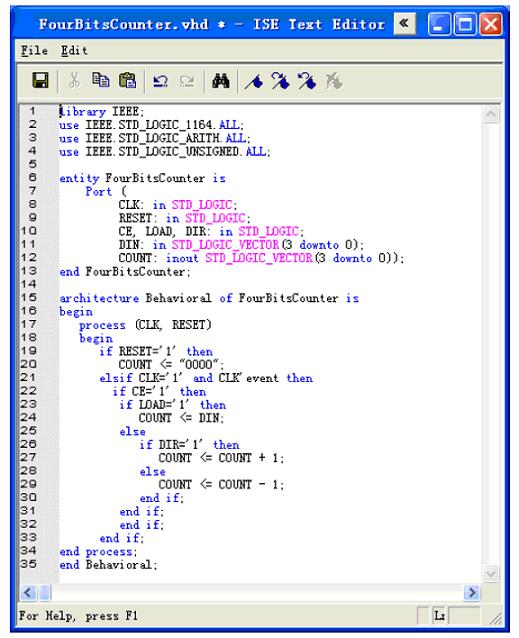

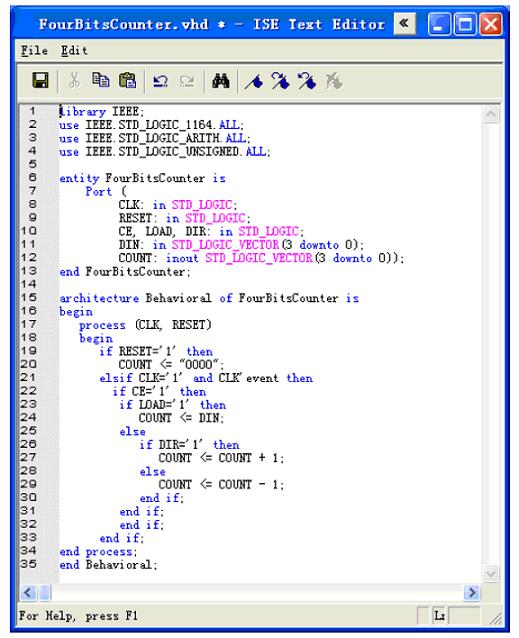

Step7. 去掉上述最后一个端口定义语句后的分号;此时的程序如图8 所示。

Step8. 选择File->Save,保存counter.vhd 源程序。

图8 修改后的计数器描述文件

5 仿真

我们可以通过设置计数器模块的输 入来观察仿真输出,以测试我们编写的VHDL 源文件是否满足逻辑功能要求。我们建立的testbench 波形将被用于与仿真软件ModelSim 的连接,用来验证所设计的计数器的功能和延时是否达到要求。

6 创建Testbench波形源文件

在仿真前,首先创建一个Testbench 波形源文件,与以前版本不同的是,该文件不是在HDL Bencher(ISE 集成的一个工具,用于设置输入波形)中打开,而是在ISE 中打开,这也是ISE6.1 不同于以前版本的地方。具体步骤如下:

Step1. 打开上一节所建立的工程;

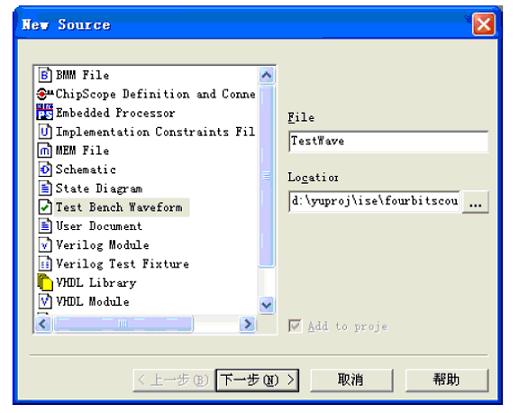

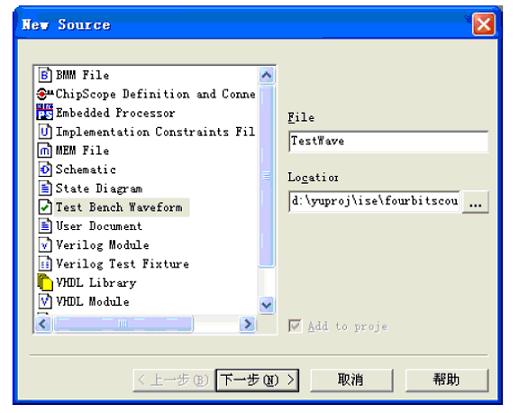

Step2. 选择Project->New Source…,(或通过在Sources in Project 中单击右键选择“NewSource…”),出现如图9 所示的窗口;

图9 创建波形源文件

Step3. 选择文件类型为Test Bench Waveform;

Step4. 键入文件名“TestWave”,如图9 中所示;

Step5. 单击“下一步”,在本步骤中可以将波形文件与VHDL 文件进行关联。

Step6. 单击“下一步”;

Step7. 单击“完成”;

Step8. 此时,HDL Bencher 程序自动启动,如图10 所示,我们可以选择哪一个信号是时钟信号并可以输入所需的时序需求;在这里我们采用系统的默认值,单击“OK”按钮;

图10 仿真时间参数的设置

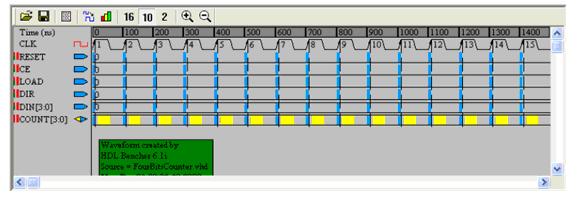

Step9. 这时出现了如图11 所示的波形;

图11 新建的波形文件

7 设置输入仿真波形

我们可以打开刚刚建立的波形文件,来初始化输入波形,步骤如下:

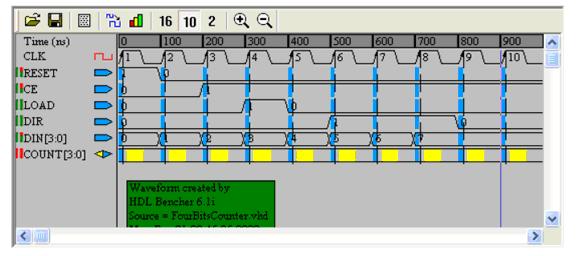

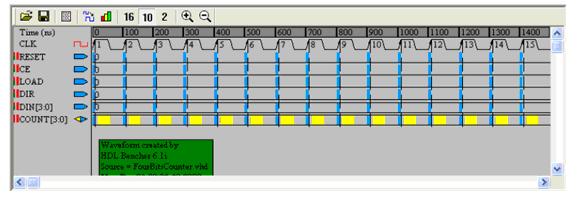

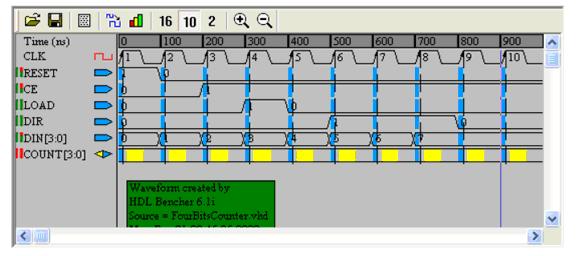

Step1. 单击波形图中的蓝色方块来设置波形电平的高低,并将仿真时间线(图中的垂直的蓝色线)拉到第10 个时钟周期处,设置后的波形如图12 所示;

图12 HDL Bencher 中输入波形的设置

Step2. 单击图12 中工具栏上的图标 ,将波形文件保存。

Step3. 查看代码覆盖率统计,单击图12 中工具栏上的图标 ,显示出代码覆盖率统计,统计结果如图13 所示。因为还没有输出,所有输出的统计均为零。代码覆盖率是一种测试术语,它可以表示运行完当前仿真时,所运行的代码占所有代码的比例。其中的 Assign 为赋值情况代码占所有代码的比例,Toggle 为上升下降沿代码占所有代码的比例。因此,代码覆盖率越高越好。

图13 代码覆盖率统计结果

在本小节我们向刚刚创建的工程中添加设计文件来实现要求的功能。按照以下步骤建立一个计数器的VHDL 文件描述。注意这里仅仅新建一个有框架的文件,下一小节将向该文件中添加具体代码。

在这里我们以一个具有复位(reset)、使能(ce)、置数(load)、计数方向控制(dir)功能的计数器为基础进行设计。其方块图如图5 所示。其中CLK 为输入计数时钟信号,系统在该信号的驱动下开始工作;RESET 为复位信号,在上升沿处,输入复位为全零;CE 为使能信号,为1 时计数正常进行,为0 时停止计数;LOAD 为置数信号,当在时钟上升沿该信号为1 时,将DIN0~DIN3 分别置给COUT0~COUT3。DIR 为计数方向控制,为1 时递增计数,为0 时递减计数。这些功能描述只是我们的设计目标,或称为设计需求,我们在设计一个系统时,第一步就是要明确我们的设计要求。

图5 计数器方块图

Step1. 选择Project->New Source;(或在Sources in Project 窗口中单击鼠标右键选择“New Source…”)出现如图6 所示的窗口;

图6 源程序的类型选择

Step2. 选择VHDL Module(VHDL 模块)作为新建源文件的类型;

Step3. 在文件名中键入“FourBitsCounter”;

Step4. 单击“下一步”;

Step5. 单击“下一步”;

Step6. 单击“完成”,完成这个新源程序的创建。新源程序文件FourBitsCounter.vhd 将会显示在HDL 编辑窗口中,它包括Library,Use,Entity,Architecture 等语句。

4 利用计数器模板向导生成设计

设计文件建立之后,我们就可以向其中填写代码了。我们可以直接书写HDL 代码,也可以利用ISE 的语言模板(ISE Language Template)工具来辅助我们书写HDL 代码。在这里我们使用语言模板,选择其中的计数器描述来完成本源程序的设计。

Step1. 选择Edit->Language Templates 打开语言模板,或者通过单击按钮 来打开语言模板,如图7 所示;

图7 计数器语言模板

Step2. 在Language Templates 中通过单击“+”来展开VHDL 下的综合模板(Synthesis Templates);

Step3. 从VHDL 综合模板中选择计数器模板(Counter Template),并把它粘贴到源程序counter.vhd 的begin 和end 之间。(或在Counter Template 上单击右键选择“Use incounter.vhd”,建议直接复制过去);

Step4. 关闭Language Templates 窗口;

Step5. 将带有注释符号“--”的计数器端口定义语句剪切并粘贴到计数器的实体(entity)描述中。这些语句如下所列:

-- CLK: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- CE, LOAD, DIR: in STD_LOGIC;

-- DIN: in STD_LOGIC_VECTOR(3 downto 0);

-- COUNT: inout STD_LOGIC_VECTOR(3 downto 0);

Step6. 去掉上述语句中的注释符号;

Step7. 去掉上述最后一个端口定义语句后的分号;此时的程序如图8 所示。

Step8. 选择File->Save,保存counter.vhd 源程序。

图8 修改后的计数器描述文件

5 仿真

我们可以通过设置计数器模块的输 入来观察仿真输出,以测试我们编写的VHDL 源文件是否满足逻辑功能要求。我们建立的testbench 波形将被用于与仿真软件ModelSim 的连接,用来验证所设计的计数器的功能和延时是否达到要求。

6 创建Testbench波形源文件

在仿真前,首先创建一个Testbench 波形源文件,与以前版本不同的是,该文件不是在HDL Bencher(ISE 集成的一个工具,用于设置输入波形)中打开,而是在ISE 中打开,这也是ISE6.1 不同于以前版本的地方。具体步骤如下:

Step1. 打开上一节所建立的工程;

Step2. 选择Project->New Source…,(或通过在Sources in Project 中单击右键选择“NewSource…”),出现如图9 所示的窗口;

图9 创建波形源文件

Step3. 选择文件类型为Test Bench Waveform;

Step4. 键入文件名“TestWave”,如图9 中所示;

Step5. 单击“下一步”,在本步骤中可以将波形文件与VHDL 文件进行关联。

Step6. 单击“下一步”;

Step7. 单击“完成”;

Step8. 此时,HDL Bencher 程序自动启动,如图10 所示,我们可以选择哪一个信号是时钟信号并可以输入所需的时序需求;在这里我们采用系统的默认值,单击“OK”按钮;

图10 仿真时间参数的设置

Step9. 这时出现了如图11 所示的波形;

图11 新建的波形文件

7 设置输入仿真波形

我们可以打开刚刚建立的波形文件,来初始化输入波形,步骤如下:

Step1. 单击波形图中的蓝色方块来设置波形电平的高低,并将仿真时间线(图中的垂直的蓝色线)拉到第10 个时钟周期处,设置后的波形如图12 所示;

图12 HDL Bencher 中输入波形的设置

Step2. 单击图12 中工具栏上的图标 ,将波形文件保存。

Step3. 查看代码覆盖率统计,单击图12 中工具栏上的图标 ,显示出代码覆盖率统计,统计结果如图13 所示。因为还没有输出,所有输出的统计均为零。代码覆盖率是一种测试术语,它可以表示运行完当前仿真时,所运行的代码占所有代码的比例。其中的 Assign 为赋值情况代码占所有代码的比例,Toggle 为上升下降沿代码占所有代码的比例。因此,代码覆盖率越高越好。

图13 代码覆盖率统计结果

ModelSim VHDL 仿真 Xilinx PCB FPGA Verilog CPLD 电容 电阻 EDA 相关文章:

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA的微处理器内核设计与实现(06-21)

- 基于PLD的纳秒级脉冲发生器(07-24)

- FPGA的八位RISC CPU的设计(07-29)

- 基于FPGA的以太网控制器设计(07-28)

- 基于FPGA的八位RISC CPU的设计(08-02)