VHDL上机手册

时间:09-26

来源:互联网

点击:

8 调用ModelSim 进行仿真简介

其实在上一节中产生预定输出时,已经使用了ModelSim,只是我们在界面上看不出来而已。这一小节我们在ISE 中调用ModelSim 进行仿真,这里讨论的仿真仍然是基于波形文件的,因此不涉及ModelSim 中过多的知识。在ModelSim 中可以进行的仿真有Simulate Behavioral Model(仿真行为模型)、Simulate Pose-Translate VHDL Model(转换后仿真)、Simulate Post-Map VHDL Model(映射后仿真)以及Simulate Post-Place&RouteVHDL Model(布局布线后仿真)。其实, 转换( Translate )、映射(Map)以及布局布线(Place&Route)是FPGA 及CPLD 设计实现时的不同阶段。

要实现一个设计,首先要进行编译或转换(Translate),转换是将HDL 描述转换为RTL 描述,转换后仿真可以认为是RTL 级仿真,而且仅仅是逻辑仿真,在仿真中不包含任何的器件、时延等信息,仅仅用于验证设计转换为RTL 级描述后是否满足功能要求;下面就是综合,在该阶段,设计文件按照约束文件与Xilinx 的原型库联系起来,映射(Map)则是将当前设计映射到具体器件的特定逻辑单元以及特定的工艺,所谓特定的逻辑单元是FPGA 中的基本的逻辑块,所谓工艺是FPGA 的制作工艺,因此,映射后仿真是将设计实现到具体器件具体逻辑单元具体工艺后进行的逻辑仿真,类似于我们制作PCB 时画完原理图后进行的仿真,此时的仿真已经考虑到了器件延时,由于没有布线,因此,连线的长度等信息就不能知道了,故此时的仿真是仅仅考虑到逻辑单元延时的仿真,而没有考虑到连线的电容、电阻、长度等信息。在亚微米(0.35 微米)以上的工艺中,连线的延时可以不太重视,而在深亚微米工艺中,连线的影响就不可小看了,为了保证深亚微米设计的成功,需要在布局布线前对设计进行时序仿真,这时候修改错误对设计进度的影响要小很多。最后是布局布线后仿真 ,为进行这个仿真,首先要进行布局布线,类似于我们对PCB 的布线,之后要进行参数提取,提取出互连线的长度、电阻、电容等信息,然后就可以根据这些信息进行仿真了,这时候的仿真中包括了器件本身的延时和互连线的延时等等部分,这种仿真也最近似实际情况。

也许读者会疑惑,有了映射后仿真为什么还需要转换后仿真呢?这是因为许多EDA 工具只能认识RTL 描述,而人们习惯使用高级的HDL描述,这就需要转换,如果转换后的RTL 描述是错误的,那么后续的过程还有什么意义呢,故还是需要进行转换后仿真的,尽管一般转换阶段不会发生什么错误。

9 调用ModelSim 进行行为仿真(Simulate Behavioral Model)

如上所述,行为仿真验证所设计的模块的功能。未涉及到设计实现中的时延等问题。具体步骤如下:

Step1. 在如图14 所示的Sources in Project 窗口中,选中TestWave 文件;

图14 Sources in Project 窗口

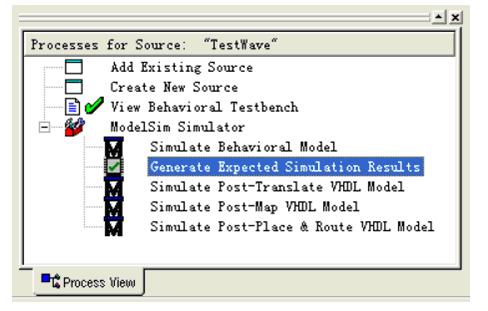

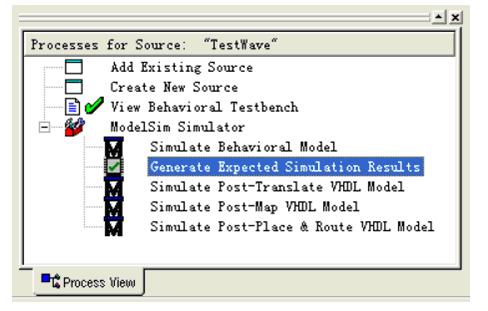

Step2. 在如图7-15 所示的Processes for Source :”TestWave”窗口中,通过单击“+”展开它;

图15 Processes for Current Source 窗口

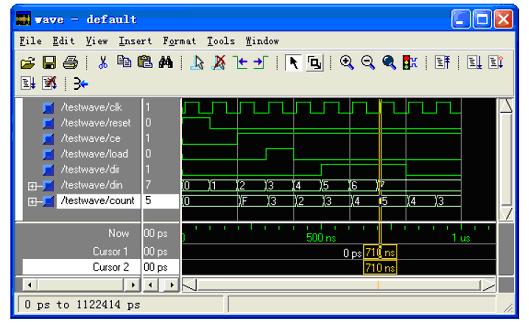

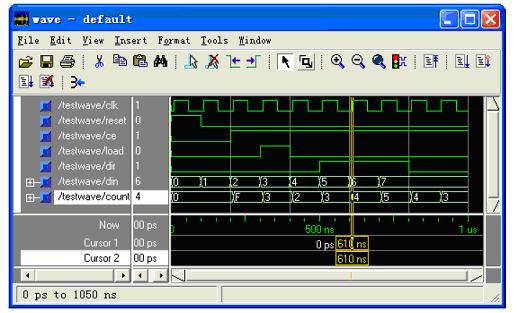

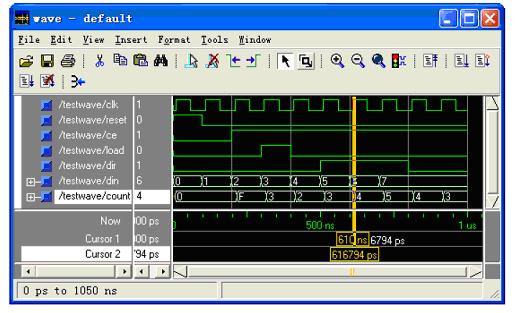

Step3. 双击Simulate Behavioral VHDL Model,ModelSim 会自动运行,仿真结果出现在ModelSim 的波形窗口(Wave Windows)中,如图16 所示,从双击命令到所有窗口的出现都是在ISE 自动创建的仿真宏文件(.fdo)的控制下来完成了,用户可以在工程存放的路径下看到该文件counter_tbw.fdo;用记事本打开该文件可以看到其内容。

图16 ModelSim 行为仿真结果

Step4. 打开波形窗口,单击按钮 ,可以将所有波形在屏幕中显示,仿真结果如图16所示。可以看到,时钟上升沿和计数值改变的时刻之间相差为零(图中两根竖线之间的间距为零)。

Step5. 关闭ModelSim 主窗口,确认退出ModelSim。

10 转换后仿真(Simulate Pose-Translate VHDL Model)

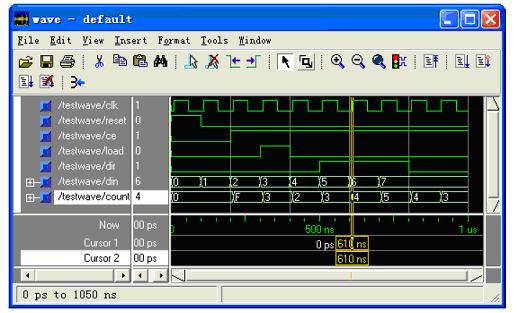

如上所述,转换后仿真是将设计转换为RTL 级描述后进行的仿真。在其中不包含实现器件的信息。具体仿真步骤与行为仿真相同。只是在第三步,双击Simulate Pose-Translate VHDLModel 就可以了。仿真波形图如图17所示。可以看到,时钟上升沿和计数值改变的时刻之间相差为零(图中两根竖线之间的间距为零)。

图17 ModelSim 转换后仿真结果

11 调用ModelSim 进行映射后仿真(Simulate Post-Map VHDL Model)

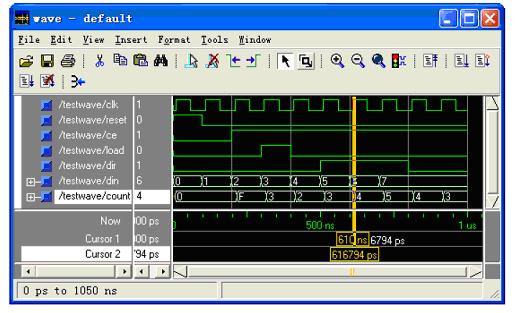

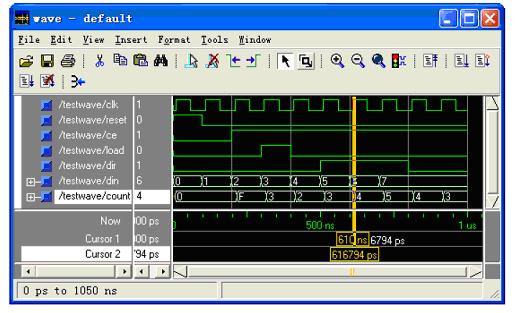

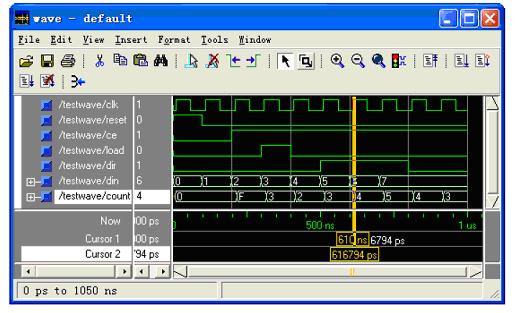

映射后仿真是设计映射到具体工艺和器件后进行的仿真,在其中包含了器件本身的延时信息。具体仿真步骤与行为仿真相同。只是在第三步,双击Simulate Post-Map VHDL Model就可以了。仿真波形图如图18 所示。可以看到,时钟上升沿和计数值改变的时刻之间相差6794ps(图中两根竖线之间的间距),说明了器件的延时为6794ps。

图18 ModelSim 映射后仿真结果

其实在上一节中产生预定输出时,已经使用了ModelSim,只是我们在界面上看不出来而已。这一小节我们在ISE 中调用ModelSim 进行仿真,这里讨论的仿真仍然是基于波形文件的,因此不涉及ModelSim 中过多的知识。在ModelSim 中可以进行的仿真有Simulate Behavioral Model(仿真行为模型)、Simulate Pose-Translate VHDL Model(转换后仿真)、Simulate Post-Map VHDL Model(映射后仿真)以及Simulate Post-Place&RouteVHDL Model(布局布线后仿真)。其实, 转换( Translate )、映射(Map)以及布局布线(Place&Route)是FPGA 及CPLD 设计实现时的不同阶段。

要实现一个设计,首先要进行编译或转换(Translate),转换是将HDL 描述转换为RTL 描述,转换后仿真可以认为是RTL 级仿真,而且仅仅是逻辑仿真,在仿真中不包含任何的器件、时延等信息,仅仅用于验证设计转换为RTL 级描述后是否满足功能要求;下面就是综合,在该阶段,设计文件按照约束文件与Xilinx 的原型库联系起来,映射(Map)则是将当前设计映射到具体器件的特定逻辑单元以及特定的工艺,所谓特定的逻辑单元是FPGA 中的基本的逻辑块,所谓工艺是FPGA 的制作工艺,因此,映射后仿真是将设计实现到具体器件具体逻辑单元具体工艺后进行的逻辑仿真,类似于我们制作PCB 时画完原理图后进行的仿真,此时的仿真已经考虑到了器件延时,由于没有布线,因此,连线的长度等信息就不能知道了,故此时的仿真是仅仅考虑到逻辑单元延时的仿真,而没有考虑到连线的电容、电阻、长度等信息。在亚微米(0.35 微米)以上的工艺中,连线的延时可以不太重视,而在深亚微米工艺中,连线的影响就不可小看了,为了保证深亚微米设计的成功,需要在布局布线前对设计进行时序仿真,这时候修改错误对设计进度的影响要小很多。最后是布局布线后仿真 ,为进行这个仿真,首先要进行布局布线,类似于我们对PCB 的布线,之后要进行参数提取,提取出互连线的长度、电阻、电容等信息,然后就可以根据这些信息进行仿真了,这时候的仿真中包括了器件本身的延时和互连线的延时等等部分,这种仿真也最近似实际情况。

也许读者会疑惑,有了映射后仿真为什么还需要转换后仿真呢?这是因为许多EDA 工具只能认识RTL 描述,而人们习惯使用高级的HDL描述,这就需要转换,如果转换后的RTL 描述是错误的,那么后续的过程还有什么意义呢,故还是需要进行转换后仿真的,尽管一般转换阶段不会发生什么错误。

9 调用ModelSim 进行行为仿真(Simulate Behavioral Model)

如上所述,行为仿真验证所设计的模块的功能。未涉及到设计实现中的时延等问题。具体步骤如下:

Step1. 在如图14 所示的Sources in Project 窗口中,选中TestWave 文件;

图14 Sources in Project 窗口

Step2. 在如图7-15 所示的Processes for Source :”TestWave”窗口中,通过单击“+”展开它;

图15 Processes for Current Source 窗口

Step3. 双击Simulate Behavioral VHDL Model,ModelSim 会自动运行,仿真结果出现在ModelSim 的波形窗口(Wave Windows)中,如图16 所示,从双击命令到所有窗口的出现都是在ISE 自动创建的仿真宏文件(.fdo)的控制下来完成了,用户可以在工程存放的路径下看到该文件counter_tbw.fdo;用记事本打开该文件可以看到其内容。

图16 ModelSim 行为仿真结果

Step4. 打开波形窗口,单击按钮 ,可以将所有波形在屏幕中显示,仿真结果如图16所示。可以看到,时钟上升沿和计数值改变的时刻之间相差为零(图中两根竖线之间的间距为零)。

Step5. 关闭ModelSim 主窗口,确认退出ModelSim。

10 转换后仿真(Simulate Pose-Translate VHDL Model)

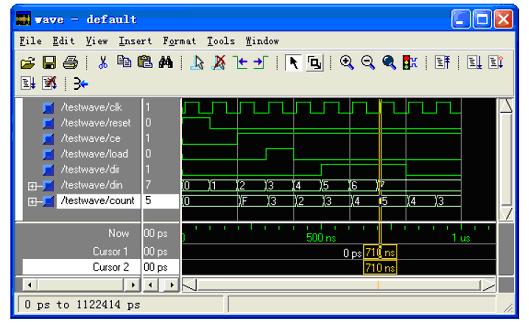

如上所述,转换后仿真是将设计转换为RTL 级描述后进行的仿真。在其中不包含实现器件的信息。具体仿真步骤与行为仿真相同。只是在第三步,双击Simulate Pose-Translate VHDLModel 就可以了。仿真波形图如图17所示。可以看到,时钟上升沿和计数值改变的时刻之间相差为零(图中两根竖线之间的间距为零)。

图17 ModelSim 转换后仿真结果

11 调用ModelSim 进行映射后仿真(Simulate Post-Map VHDL Model)

映射后仿真是设计映射到具体工艺和器件后进行的仿真,在其中包含了器件本身的延时信息。具体仿真步骤与行为仿真相同。只是在第三步,双击Simulate Post-Map VHDL Model就可以了。仿真波形图如图18 所示。可以看到,时钟上升沿和计数值改变的时刻之间相差6794ps(图中两根竖线之间的间距),说明了器件的延时为6794ps。

图18 ModelSim 映射后仿真结果

ModelSim VHDL 仿真 Xilinx PCB FPGA Verilog CPLD 电容 电阻 EDA 相关文章:

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA的微处理器内核设计与实现(06-21)

- 基于PLD的纳秒级脉冲发生器(07-24)

- FPGA的八位RISC CPU的设计(07-29)

- 基于FPGA的以太网控制器设计(07-28)

- 基于FPGA的八位RISC CPU的设计(08-02)