VHDL上机手册

时间:09-26

来源:互联网

点击:

1 ISE 软件的运行及ModelSim 的配置

2 创建一个新工程

3 创建一个VHDL源文件框架

4 利用计数器模板向导生成设计

*5 仿真

6 创建Testbench波形源文件

7 设置输入仿真波形

*8 调用ModelSim 进行仿真简介

9 调用ModelSim 进行行为仿真(Simulate Behavioral Model)

10 转换后仿真(Simulate Pose-Translate VHDL Model)

11 调用ModelSim 进行映射后仿真(Simulate Post-Map VHDL Model)

12 布局布线后的仿真( Simulate Post-Place&Route VHDL Model)

1. ISE 软件的运行及ModelSim 的配置

单击“开始->程序->Xilinx ISE6->Project Navigator”,进入ISE 软件。

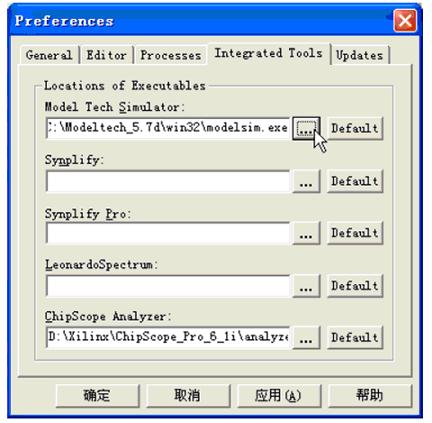

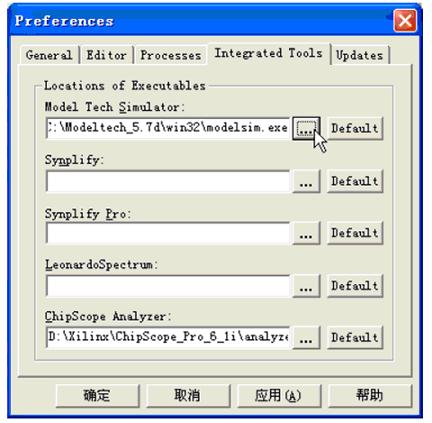

为了能够使用ModelSim 进行仿真,选择菜单Edit->Preferences…,选择选项卡Partner Tools,出现界面如图1 所示。单击按钮 找出ModelSim.exe 文件,单击“确定”。需要注意的是这方面的设置与以前ISE 版本不同,在ISE4.2 中设置是这样的。但在ISE5.1 以及ISE5.2 中是指定ModelSim.exe 文件所在的目录,而ISE6.1 的设置与ISE4.2 的设置相同。单击“确定”关闭该窗口,关闭ISE(这一步非常重要,否则可能不能在ISE 中调用ModelSim 进行仿真),再重新进入ISE 既可用调用ModelSim 对设计进行仿真了。

图1 第三方工具设置窗口

2 创建一个新工程

Step1. 单击“开始->程序->Xilinx ISE6->Project Navigator”,进入ISE 软件。

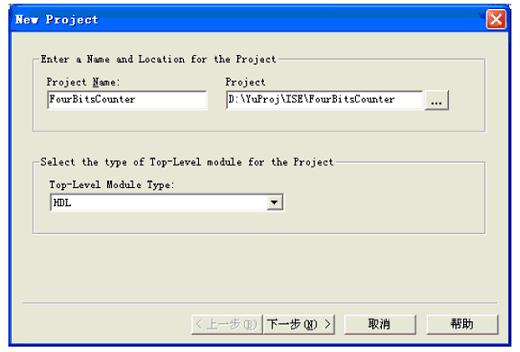

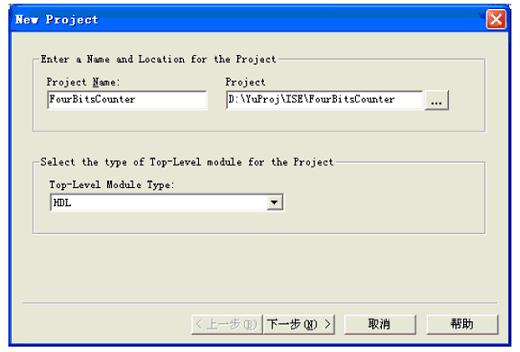

Step2. 选择File->New Project…,出现如图2 所示的窗口。这个窗口与以前版本的差别较大,以前的版本出现的窗口中可以直接选取器件类型、封装、门数、速度等级等信息。而在ISE6.1 中需要单击“下一步”才能看到这些设置信息。在本例中,我们先选择工程存放的路径,然后输入工程名称。系统自动为每一个工程设定一个目录,目录名为工程名。再选择顶层模块类型为HDL。

图2 新工程项对话框

(其他几种类型说明如下:Schematic为原理图输入类型,类似于我们制作PCB 原理图时的情况,可以从库中选取器件,也可以用HDL 语言来生成器件,在后续章节会介绍原理图为设计输入的情况;EDIF为网表输入类型,EDIF 是Electronic Data Interchange Format 的缩写,是一种描述设计网表的标准的工业文件格式,可以由第三方工具生成,在ISE 中可以将其作为一种标准的输入格式。NGC 文件是一种包含了逻辑设计数据和约束的网表,所谓约束是指FPGA 设计中的一些特定的要求,例如,我们分配设计中的信号到具体的管脚时,需要一个文件来指定如何分配,这就是一种约束文件,由于NGC 网表包含了设计和约束,因此一个文件足够描述一个设计了。NGC/NGO 和EDIF 都可以在ISE 外由其他综合工具生成也可由ISE 生成。如果我们需要用ISE 作为设计输入,需要选择Schematic 或HDL 作为顶层模块类型;如果已经完成的设计文件为ABEL、Verilog或VHDL,应选择HDL 为顶层模块类型;如果已经完成的设计文件为原理图,这里应该选择Schematic 作为顶层模块类型。)

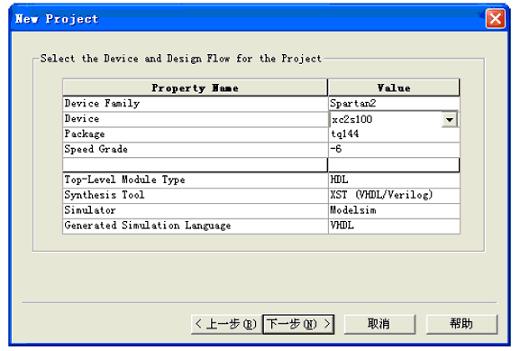

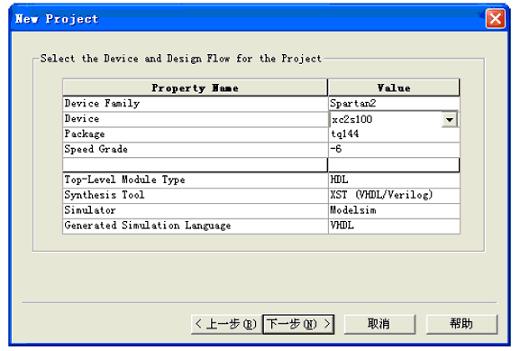

Step3. 单击“下一步”,出现如图3 所示的窗口,在该窗口中来选择设计实现时所用的器件。在包含FPGA 的PCB 板子做出来以前,我们选择不同类型的FPGA 进行测试,看看FPGA 的资源是否够用,在PCB 板子做出来以后,我们在这里的选择与PCB板上的FPGA 必须一致。否则生成的下载文件无法配置到FPGA 中。此处若选择错了,也没有关系,因为后面可以随时修改这些设置。其中DeviceFamily 表示目标器件的类型;Device 表示目标器件的具体型号;Package 表示器件的封装;SpeedGrade 表示器件的速度等级。这里我们选择器件为Spartan2E,xc2s100,tq144,-6。其中xc2s100中的100 表示器件为10 万门,tq144 表示器件有144 个管脚。

图3 设置工程所用的器件参数

Step4. 因为这里我们重新编写VHDL 源代码,而不是使用以前设计好的源代码,故再单击“下一步”,“下一步”,单击“完成”,工程创建完毕。

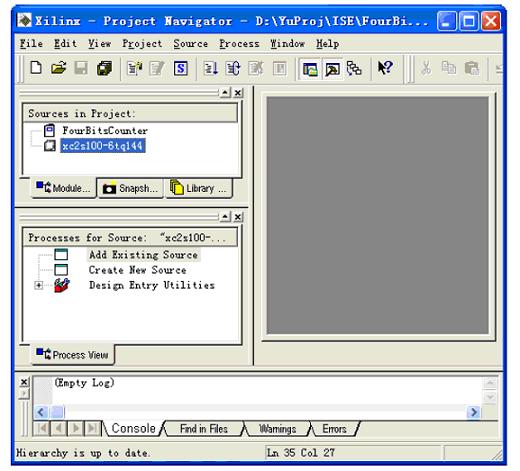

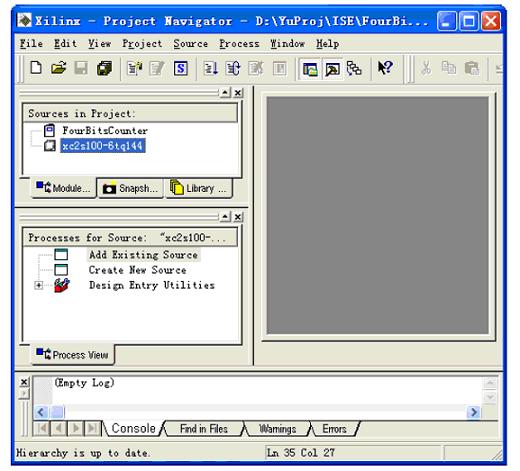

Step5. 这时的界面如图4 所示,这里需要关注的是界面左上角出现的小框为我们所有的源文件的管理窗口,在其下面的窗口为我们选择不同的源文件时其所有可能操作的显示窗口;右半部分窗口为我们设计输入代码的窗口;下面的窗口为编译等信息的显示窗口。这里与以前版本不同的地方在于编译输入窗口这里将Warnings 和Errors 可以分开显示。我们可以在输入不同文件后选中不同的文件,看看进程窗口中的变化。这样,我们新建了一个工程,下一步就要在工程中输入一些设计文件来实现我们的设计。

图4 创建新工程后的ISE 界面

2 创建一个新工程

3 创建一个VHDL源文件框架

4 利用计数器模板向导生成设计

*5 仿真

6 创建Testbench波形源文件

7 设置输入仿真波形

*8 调用ModelSim 进行仿真简介

9 调用ModelSim 进行行为仿真(Simulate Behavioral Model)

10 转换后仿真(Simulate Pose-Translate VHDL Model)

11 调用ModelSim 进行映射后仿真(Simulate Post-Map VHDL Model)

12 布局布线后的仿真( Simulate Post-Place&Route VHDL Model)

1. ISE 软件的运行及ModelSim 的配置

单击“开始->程序->Xilinx ISE6->Project Navigator”,进入ISE 软件。

为了能够使用ModelSim 进行仿真,选择菜单Edit->Preferences…,选择选项卡Partner Tools,出现界面如图1 所示。单击按钮 找出ModelSim.exe 文件,单击“确定”。需要注意的是这方面的设置与以前ISE 版本不同,在ISE4.2 中设置是这样的。但在ISE5.1 以及ISE5.2 中是指定ModelSim.exe 文件所在的目录,而ISE6.1 的设置与ISE4.2 的设置相同。单击“确定”关闭该窗口,关闭ISE(这一步非常重要,否则可能不能在ISE 中调用ModelSim 进行仿真),再重新进入ISE 既可用调用ModelSim 对设计进行仿真了。

图1 第三方工具设置窗口

2 创建一个新工程

Step1. 单击“开始->程序->Xilinx ISE6->Project Navigator”,进入ISE 软件。

Step2. 选择File->New Project…,出现如图2 所示的窗口。这个窗口与以前版本的差别较大,以前的版本出现的窗口中可以直接选取器件类型、封装、门数、速度等级等信息。而在ISE6.1 中需要单击“下一步”才能看到这些设置信息。在本例中,我们先选择工程存放的路径,然后输入工程名称。系统自动为每一个工程设定一个目录,目录名为工程名。再选择顶层模块类型为HDL。

图2 新工程项对话框

(其他几种类型说明如下:Schematic为原理图输入类型,类似于我们制作PCB 原理图时的情况,可以从库中选取器件,也可以用HDL 语言来生成器件,在后续章节会介绍原理图为设计输入的情况;EDIF为网表输入类型,EDIF 是Electronic Data Interchange Format 的缩写,是一种描述设计网表的标准的工业文件格式,可以由第三方工具生成,在ISE 中可以将其作为一种标准的输入格式。NGC 文件是一种包含了逻辑设计数据和约束的网表,所谓约束是指FPGA 设计中的一些特定的要求,例如,我们分配设计中的信号到具体的管脚时,需要一个文件来指定如何分配,这就是一种约束文件,由于NGC 网表包含了设计和约束,因此一个文件足够描述一个设计了。NGC/NGO 和EDIF 都可以在ISE 外由其他综合工具生成也可由ISE 生成。如果我们需要用ISE 作为设计输入,需要选择Schematic 或HDL 作为顶层模块类型;如果已经完成的设计文件为ABEL、Verilog或VHDL,应选择HDL 为顶层模块类型;如果已经完成的设计文件为原理图,这里应该选择Schematic 作为顶层模块类型。)

Step3. 单击“下一步”,出现如图3 所示的窗口,在该窗口中来选择设计实现时所用的器件。在包含FPGA 的PCB 板子做出来以前,我们选择不同类型的FPGA 进行测试,看看FPGA 的资源是否够用,在PCB 板子做出来以后,我们在这里的选择与PCB板上的FPGA 必须一致。否则生成的下载文件无法配置到FPGA 中。此处若选择错了,也没有关系,因为后面可以随时修改这些设置。其中DeviceFamily 表示目标器件的类型;Device 表示目标器件的具体型号;Package 表示器件的封装;SpeedGrade 表示器件的速度等级。这里我们选择器件为Spartan2E,xc2s100,tq144,-6。其中xc2s100中的100 表示器件为10 万门,tq144 表示器件有144 个管脚。

图3 设置工程所用的器件参数

Step4. 因为这里我们重新编写VHDL 源代码,而不是使用以前设计好的源代码,故再单击“下一步”,“下一步”,单击“完成”,工程创建完毕。

Step5. 这时的界面如图4 所示,这里需要关注的是界面左上角出现的小框为我们所有的源文件的管理窗口,在其下面的窗口为我们选择不同的源文件时其所有可能操作的显示窗口;右半部分窗口为我们设计输入代码的窗口;下面的窗口为编译等信息的显示窗口。这里与以前版本不同的地方在于编译输入窗口这里将Warnings 和Errors 可以分开显示。我们可以在输入不同文件后选中不同的文件,看看进程窗口中的变化。这样,我们新建了一个工程,下一步就要在工程中输入一些设计文件来实现我们的设计。

图4 创建新工程后的ISE 界面

ModelSim VHDL 仿真 Xilinx PCB FPGA Verilog CPLD 电容 电阻 EDA 相关文章:

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA的微处理器内核设计与实现(06-21)

- 基于PLD的纳秒级脉冲发生器(07-24)

- FPGA的八位RISC CPU的设计(07-29)

- 基于FPGA的以太网控制器设计(07-28)

- 基于FPGA的八位RISC CPU的设计(08-02)