利用Altera增强型配置片实现FPGA动态配置

时间:09-16

来源:互联网

点击:

4.2 Flash存储器

不同配置片内部Flash容量不同。EPCI6有16Mbit容量,而EPC8、EPC4分别只有8 Mbit、4 Mbit,。Flash存储器分成三个块存储区,分别为启动块、参数块和配置数据块存储区。每个块存储区都有自己独立的保护机制并能单独进行擦除。下面将分别阐述各个块的功能。

(1) 启动块

以EPC16为例,启动块大小为16 KB,可用它替代微处理器专用PROM,也可用于存储其他系统的数据。启动块的保护机制由配置片RP引脚、WR引脚和块锁存位共同确定。

(2)参数块

参数块用来存储少量而需频繁更新的参数。EPCI6有6个参数块,每块为8 KB。参数块的保护机制是由配置

片RP引脚和块锁存位共同确定。

(3) 配置数据块

EPC片内Flash上除启动块和参数块之外的空间均为配置块存储区。可用于存储配置数据和作为用户的存储空间。EPC16有31块64 KB的配置块。和参数块一样,配置块的保护机制也由配置片RP引脚和块锁存位共同确定。

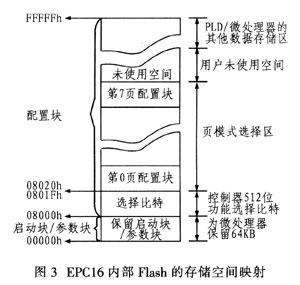

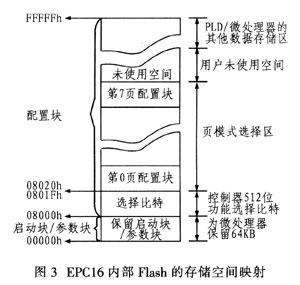

4.2.1 Flash内存映射

EPCI6的内存映射分为两部分:配置控制器存储空间和用户存储空间。配置摔制器存储空间由控制器功能选择比特和8页配置数据组成。其起始地址是08000h (在64 KB的启动块/参数块后)。08000h~0801Fh地址范围是保留的控制器功能选择比特空间。图3是EPCI6内部Flash的存储空间映射。

4.2.2页模式选择

页模式选择功能使配置片最多可存储8页不同的PLD配置数据,并由用户选择页号配置不同的PLD。页模式选择需要由软件和硬件配合实现。硬件上通过设定配置片PGM[2:0]引脚(PGM是最高位)电平决定页号。同时在用QuatrusⅡ编译程序时修改编译文件的属性为所选择页号。第0页是默认的配置页。

4.2.3配置片工作模式

配置片有两种工作模式:正常模式和编程模式。

(1) 正常模式

正常模式是使用配置片内Flash中的压缩数据实现PLD配置。整个过程包括从Flash读出数据、数据解压和传输数据到PLD。

上电时,上电复位电路(POR)产生所有复位信号。该电路用10 MHz内部默认时钟复位配置片内控制单元。在开始配置前,配置片采样PGM[2:0]引脚上的电平值以确定从Flash的配置块内读取配置数据的页号。控制单元根据Flash中的选择比特值重新配置系统内部时钟。此后开始从配置块内读出压缩数据。当配置片的OE引脚变为高电平时,压缩引擎(PCU)输出DCLK时钟,开始传输配置数据到PLD。

当所选配置块内的最后一个比特从Flash读出后,配置片内部页计数器溢出,压缩引擎停止读Flash数据。若PLD正确接收所有配置数据(PLD拉高nCONF_DONE引脚),nCS引脚将被拉高,说明一次成功配置过程结束。若未正确接收数据(PLD拉低nCONF_DONE引脚),上电复位电路拉低OE引脚并重新配置。配置结束,压缩引擎(PCU)停止输出DCLK时钟。

(2) 编程模式

当用JTAG通过配置片内JTAG接口单元进行配置PLD时,配置片处于编程模式。由于本文采用正常模式,故不详细阐述。

5 接口电路设计与实现

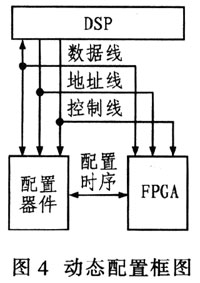

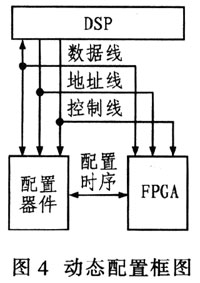

图4、图5所示分别为笔者参与的某项目中与动态配置相关部分的框图和电路图。

如图4所示,为避免对传统配置电路做较大改动。本动态配置方案未采用由:DSP直接动态配置FPGA的方式,而是将配置时序由配置片承担。在FPGA处于用户模式时。若配置片nCONFIG引脚为低电平,将会触发FPGA重新进行一次配置。从而实现动态配置。

具体过程为:

(1)在FPGA处于用户模式时,配置片内Flash处于可读写状态。DSP将需要更新的代码在此模式下写入Flash相应的配置数据块内。

(2)在FPGA内设置一个1比特位宽配置寄存器。DSP写入配置命令,当其值为1时。EPC_jTAG_nlNIT(FPGA的一个I/0)引脚配置O。由于此引脚连接FPGA的nCONFIG引脚,故FPGA将由用户模式进人复位状态,nSTATUS引脚输出低电平从而使配置片复位。复位结束后将开始启动一次新的配置。

不同配置片内部Flash容量不同。EPCI6有16Mbit容量,而EPC8、EPC4分别只有8 Mbit、4 Mbit,。Flash存储器分成三个块存储区,分别为启动块、参数块和配置数据块存储区。每个块存储区都有自己独立的保护机制并能单独进行擦除。下面将分别阐述各个块的功能。

(1) 启动块

以EPC16为例,启动块大小为16 KB,可用它替代微处理器专用PROM,也可用于存储其他系统的数据。启动块的保护机制由配置片RP引脚、WR引脚和块锁存位共同确定。

(2)参数块

参数块用来存储少量而需频繁更新的参数。EPCI6有6个参数块,每块为8 KB。参数块的保护机制是由配置

片RP引脚和块锁存位共同确定。

(3) 配置数据块

EPC片内Flash上除启动块和参数块之外的空间均为配置块存储区。可用于存储配置数据和作为用户的存储空间。EPC16有31块64 KB的配置块。和参数块一样,配置块的保护机制也由配置片RP引脚和块锁存位共同确定。

4.2.1 Flash内存映射

EPCI6的内存映射分为两部分:配置控制器存储空间和用户存储空间。配置摔制器存储空间由控制器功能选择比特和8页配置数据组成。其起始地址是08000h (在64 KB的启动块/参数块后)。08000h~0801Fh地址范围是保留的控制器功能选择比特空间。图3是EPCI6内部Flash的存储空间映射。

4.2.2页模式选择

页模式选择功能使配置片最多可存储8页不同的PLD配置数据,并由用户选择页号配置不同的PLD。页模式选择需要由软件和硬件配合实现。硬件上通过设定配置片PGM[2:0]引脚(PGM是最高位)电平决定页号。同时在用QuatrusⅡ编译程序时修改编译文件的属性为所选择页号。第0页是默认的配置页。

4.2.3配置片工作模式

配置片有两种工作模式:正常模式和编程模式。

(1) 正常模式

正常模式是使用配置片内Flash中的压缩数据实现PLD配置。整个过程包括从Flash读出数据、数据解压和传输数据到PLD。

上电时,上电复位电路(POR)产生所有复位信号。该电路用10 MHz内部默认时钟复位配置片内控制单元。在开始配置前,配置片采样PGM[2:0]引脚上的电平值以确定从Flash的配置块内读取配置数据的页号。控制单元根据Flash中的选择比特值重新配置系统内部时钟。此后开始从配置块内读出压缩数据。当配置片的OE引脚变为高电平时,压缩引擎(PCU)输出DCLK时钟,开始传输配置数据到PLD。

当所选配置块内的最后一个比特从Flash读出后,配置片内部页计数器溢出,压缩引擎停止读Flash数据。若PLD正确接收所有配置数据(PLD拉高nCONF_DONE引脚),nCS引脚将被拉高,说明一次成功配置过程结束。若未正确接收数据(PLD拉低nCONF_DONE引脚),上电复位电路拉低OE引脚并重新配置。配置结束,压缩引擎(PCU)停止输出DCLK时钟。

(2) 编程模式

当用JTAG通过配置片内JTAG接口单元进行配置PLD时,配置片处于编程模式。由于本文采用正常模式,故不详细阐述。

5 接口电路设计与实现

图4、图5所示分别为笔者参与的某项目中与动态配置相关部分的框图和电路图。

如图4所示,为避免对传统配置电路做较大改动。本动态配置方案未采用由:DSP直接动态配置FPGA的方式,而是将配置时序由配置片承担。在FPGA处于用户模式时。若配置片nCONFIG引脚为低电平,将会触发FPGA重新进行一次配置。从而实现动态配置。

具体过程为:

(1)在FPGA处于用户模式时,配置片内Flash处于可读写状态。DSP将需要更新的代码在此模式下写入Flash相应的配置数据块内。

(2)在FPGA内设置一个1比特位宽配置寄存器。DSP写入配置命令,当其值为1时。EPC_jTAG_nlNIT(FPGA的一个I/0)引脚配置O。由于此引脚连接FPGA的nCONFIG引脚,故FPGA将由用户模式进人复位状态,nSTATUS引脚输出低电平从而使配置片复位。复位结束后将开始启动一次新的配置。

电路 嵌入式 FPGA 无线电 Altera 电阻 电压 振荡器 电路图 DSP 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)