利用Altera增强型配置片实现FPGA动态配置

时间:09-16

来源:互联网

点击:

1. 引言

在当今复杂数字电路设计中,大多采用以"嵌入式微控制器+FPGA"为核心的体系结构此体系结构中FPGA配置效率和灵活性的差异影响了产品的开周期和产品升级的易施性。传统的FPGA配置方案(例如调试阶段的专用下载电缆方式。成品阶段的专用配置片方式)在成本、效率、灵活性方面都存在着明显不足。针对这样的实际问题,基于嵌入式微控制器与FPGA广泛共存于复杂数字系统的背景,借鉴软件无线电"一机多能"的思想,提出了一种对现有传统FPGA配置方案硬件电路稍做调整并增加部分软件功能。即可实现FPGA动态配置的方案。本文将在介绍Altera公司Stratix系列FPGA配置模式、FPGA配置流程、增强型配置片内部工作原理的基础上给出利用EPCI6实现FPGA动态配置的方案。并给出软硬件接口电路。

2 FPGA配置方式

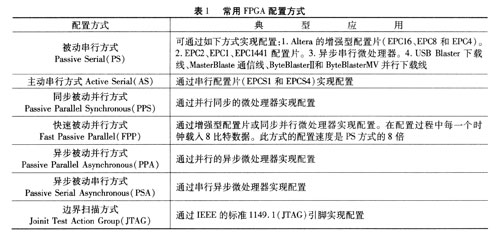

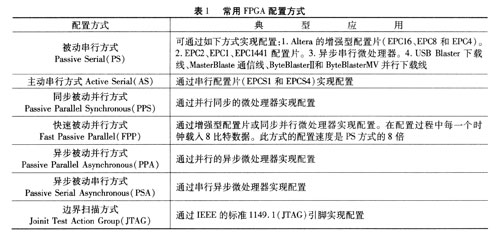

可编程器件的配置方式分为主动配置和被动配置两类。主动配置由可编程器件引导配置过程,被动配置则由外部处理器控制配置过程。 根据配置数据线数,器件配置可分为并行配置和串行配置两类。串行配置以Bit(比特)为单位将配置数据载人可编程器件:而并行配置一般以Byte(

字节)为单位向可编程器件载入配置数据。被动配置根据配置数据与时钟的关系可分为同步和异步两种方式。

表1列举了Altera公司常用FPGA(Stratix、Cyclone、APEXⅡ、APEX20K、Mercury、ACE XK、FLEXlOK和FLEX6000)的配置方式。

3 FPGA配置流程

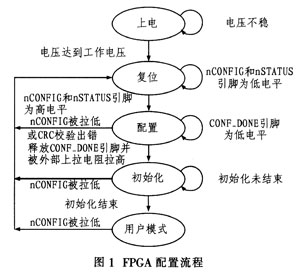

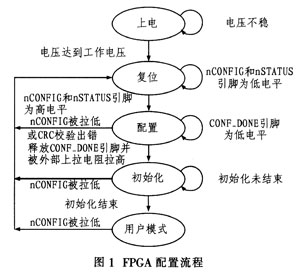

FPGA的配置数据存储在内部SRAM单元中。由于SRAM掉电后配置数据会丢失,因此每次上电时必须重新将配置数据写入SRAM中。这个过程称为FPGA的配置。FPGA配置过程如图1所示。表2为Stratix配置引脚定义。

(1) 上电

上电过程中FPGA内部状态机被复位,nSTA-TUS和CONF_DONE引脚由FPGA置为低电平,所有I/O引脚为三态且FPGA内部配置寄存器被清空。

(2) 复位

当nCONFIG或nSTATUS引脚为低电平时,FPGA进入复位状态。在此状态下,FPGA采样MSEL引脚的电平值,以确定采用的配置方式。同时nSTATUS和CONF_DONE引脚被拉低,所有I/O引脚三态并且FPGA内部配置寄存器被清空。

(3) 配置

当nCONFIG为高电平,nSTATUS被FPGA释放并由外部上拉电阻拉为高电平后进入配置状态。此状态下配置数据在DCLK时钟的上升沿载入FP-GA。若正确接收所有配置数据(CRC校验无误)。FPGA释放CONF_DONE引脚且当其被外部上拉电阻拉高后进入初始化状态。

(4) 初始化

此状态下FPGA内部逻辑和寄存器被初始化:使能I/0缓冲,释放INIT_DONE引脚(可选)。

(5) 用户模式

在此状态下FPGA开始执行用户程序。

4 增强型配置片工作原理

Ahera公司增强型配置片支持在一块配置片上进行多块高密度PLD(Programmable Logic De-vice)配置。配置片主要由两大核心模块构成一控制器和Flash存储器。存储空间除用于存储配置数据外,未使用的部分可用于微处理器或PLD的外部存储器。下面将分别阐述增强型配置片的核心模块。

4.1 增强型配置片控制单元

控制单元由以下子模块构成:

(1) 上电复位电路(POR)

在电源电压未达到需要的稳定电压时此模块将使配置片处于复位状态。有两种上电复位时间可选,100 mS,和2 mS,。配置片PORSEL引脚决定复位时间长短。此引脚为低电平时复位时间为100 ms,反之为2 ms。

(2) 内部振荡器(IOSC)

内部振荡器有四种模式(四个不同频率),可通过编译FPGA代码在OuatrusⅡ软件中选择。

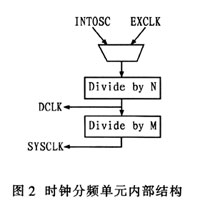

(3) 时钟分频单元(CDU)

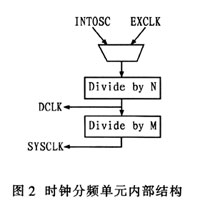

时钟分频单元对内部振荡器产生的时钟或外部输入时钟进行分频,得到配置片内部系统时钟SYSCLK和外部数据输出时钟DCLK。其内部有两个分频器,一个分频器的分频系数为N,产生DCLK信号;另一个分频器的分频系数为M,产生SYSCLK信号。其内部结构如图2所示。

上电后配置片默认采用内部振荡器中A模式,振荡频率为8 MHzo其中,一个分频器分频系数为1。另一个分频器分频系数为2。

(4) 压缩引擎(PCU)

增强型配置片支持数据压缩。数据压缩由QuatrusⅡ软件实现,解压由压缩引擎实现。压缩后的数据存储在内部Flash中。配置过程中压缩引擎解压从Flash读出的数据。这一特性极大地增强了配置片的有效使用空间。以EPCI6为例,通过数据压缩可存储30 Mbit数据。

(5) PLD配置单元

PLD配置单元负责传输解压后的数据到PLD。它支持四种并行配置模式,即可将解压数据按1比特、2比特、4比特或8比特输出。根据预先配置的配置模式,PLD配置单元将数据移位输出到有效数据引脚上。无用的数据引脚输出低电平。

(6) JTAG接口单元(JIU)

由于本文未采用JTAG实现FPGA动态配置,故此单元不做详细介绍。

在当今复杂数字电路设计中,大多采用以"嵌入式微控制器+FPGA"为核心的体系结构此体系结构中FPGA配置效率和灵活性的差异影响了产品的开周期和产品升级的易施性。传统的FPGA配置方案(例如调试阶段的专用下载电缆方式。成品阶段的专用配置片方式)在成本、效率、灵活性方面都存在着明显不足。针对这样的实际问题,基于嵌入式微控制器与FPGA广泛共存于复杂数字系统的背景,借鉴软件无线电"一机多能"的思想,提出了一种对现有传统FPGA配置方案硬件电路稍做调整并增加部分软件功能。即可实现FPGA动态配置的方案。本文将在介绍Altera公司Stratix系列FPGA配置模式、FPGA配置流程、增强型配置片内部工作原理的基础上给出利用EPCI6实现FPGA动态配置的方案。并给出软硬件接口电路。

2 FPGA配置方式

可编程器件的配置方式分为主动配置和被动配置两类。主动配置由可编程器件引导配置过程,被动配置则由外部处理器控制配置过程。 根据配置数据线数,器件配置可分为并行配置和串行配置两类。串行配置以Bit(比特)为单位将配置数据载人可编程器件:而并行配置一般以Byte(

字节)为单位向可编程器件载入配置数据。被动配置根据配置数据与时钟的关系可分为同步和异步两种方式。

表1列举了Altera公司常用FPGA(Stratix、Cyclone、APEXⅡ、APEX20K、Mercury、ACE XK、FLEXlOK和FLEX6000)的配置方式。

3 FPGA配置流程

FPGA的配置数据存储在内部SRAM单元中。由于SRAM掉电后配置数据会丢失,因此每次上电时必须重新将配置数据写入SRAM中。这个过程称为FPGA的配置。FPGA配置过程如图1所示。表2为Stratix配置引脚定义。

(1) 上电

上电过程中FPGA内部状态机被复位,nSTA-TUS和CONF_DONE引脚由FPGA置为低电平,所有I/O引脚为三态且FPGA内部配置寄存器被清空。

(2) 复位

当nCONFIG或nSTATUS引脚为低电平时,FPGA进入复位状态。在此状态下,FPGA采样MSEL引脚的电平值,以确定采用的配置方式。同时nSTATUS和CONF_DONE引脚被拉低,所有I/O引脚三态并且FPGA内部配置寄存器被清空。

(3) 配置

当nCONFIG为高电平,nSTATUS被FPGA释放并由外部上拉电阻拉为高电平后进入配置状态。此状态下配置数据在DCLK时钟的上升沿载入FP-GA。若正确接收所有配置数据(CRC校验无误)。FPGA释放CONF_DONE引脚且当其被外部上拉电阻拉高后进入初始化状态。

(4) 初始化

此状态下FPGA内部逻辑和寄存器被初始化:使能I/0缓冲,释放INIT_DONE引脚(可选)。

(5) 用户模式

在此状态下FPGA开始执行用户程序。

4 增强型配置片工作原理

Ahera公司增强型配置片支持在一块配置片上进行多块高密度PLD(Programmable Logic De-vice)配置。配置片主要由两大核心模块构成一控制器和Flash存储器。存储空间除用于存储配置数据外,未使用的部分可用于微处理器或PLD的外部存储器。下面将分别阐述增强型配置片的核心模块。

4.1 增强型配置片控制单元

控制单元由以下子模块构成:

(1) 上电复位电路(POR)

在电源电压未达到需要的稳定电压时此模块将使配置片处于复位状态。有两种上电复位时间可选,100 mS,和2 mS,。配置片PORSEL引脚决定复位时间长短。此引脚为低电平时复位时间为100 ms,反之为2 ms。

(2) 内部振荡器(IOSC)

内部振荡器有四种模式(四个不同频率),可通过编译FPGA代码在OuatrusⅡ软件中选择。

(3) 时钟分频单元(CDU)

时钟分频单元对内部振荡器产生的时钟或外部输入时钟进行分频,得到配置片内部系统时钟SYSCLK和外部数据输出时钟DCLK。其内部有两个分频器,一个分频器的分频系数为N,产生DCLK信号;另一个分频器的分频系数为M,产生SYSCLK信号。其内部结构如图2所示。

上电后配置片默认采用内部振荡器中A模式,振荡频率为8 MHzo其中,一个分频器分频系数为1。另一个分频器分频系数为2。

(4) 压缩引擎(PCU)

增强型配置片支持数据压缩。数据压缩由QuatrusⅡ软件实现,解压由压缩引擎实现。压缩后的数据存储在内部Flash中。配置过程中压缩引擎解压从Flash读出的数据。这一特性极大地增强了配置片的有效使用空间。以EPCI6为例,通过数据压缩可存储30 Mbit数据。

(5) PLD配置单元

PLD配置单元负责传输解压后的数据到PLD。它支持四种并行配置模式,即可将解压数据按1比特、2比特、4比特或8比特输出。根据预先配置的配置模式,PLD配置单元将数据移位输出到有效数据引脚上。无用的数据引脚输出低电平。

(6) JTAG接口单元(JIU)

由于本文未采用JTAG实现FPGA动态配置,故此单元不做详细介绍。

电路 嵌入式 FPGA 无线电 Altera 电阻 电压 振荡器 电路图 DSP 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)