Flash 编程器的FPGA实现

时间:09-15

来源:互联网

点击:

1 引言

闪速存储器(FLASH Memory)以其集成度高、成本低、使用方便等许多优点,广泛应用于通讯设备、办公设备、家用电器、医疗设备等领域。利用其保存信息的非易失性和在线更新数据参数的特性,可将其作为具有一定灵活性的只读存储器(ROM)使用。

现在的数字电路应用系统设计中,经常遇到大容量的数据存储问题。Flash由于容量大、存储速度快、体积小、功耗低等诸多优点,而成为应用系统中数据存储器件的首选。由于在研制实时信号处理系统时,需要一块大容量的Flash来存储坐标变换的数据作查找表,因此面临一个如何对Flash进行编程,将数据写入Flash的问题。由于我们选用的Flash芯片为SST39SF010/020,是最新生产的型号,需要自己开发编程器来满足设计需要,达到既经济又实用的目的。这一型号的Flash采用的是标准的5V电压供电,器件在命令控制下自己产生内部的擦除电压Vpp,从而完成数据的写入和芯片的擦除等各种功能。而FPGA这种大规模的可编程器件十分适合逻辑电路的设计,能方便地控制和产生 Flash编程操作中的各种控制命令,实现编程器的功能。

2 Flash的性能参数和操作时序

以最新的Flash芯片型号SST39SF010/020为例,容量为1/2Mbit(×8)。 它的主要性能有:

● 单一的5.0V电压读写操作;

● 高可靠性,超过100年的数据保持能力;

● 快速擦除和字节编程功能

——扇区擦除时间典型值只需7ms;

——片擦除时间典型值只需15ms;

——字节编程需时间典型值只需20微秒;

——片重写时间需3ms(SST39SF010)

● 片内部产生Vpp编程电压,实现自动读写时序;

● I/O兼容TTL;

各引脚功能:

Ams~A0:地址输入 ——提供存储器地址;

DQ7~DQ0:数据输入/输出 ——在读时序时输出数据,在写时序时接收输入的数据;

CE#:片选使能——当CE#为低电平有效;

OE#:输出使能——选通输出缓存器;

WE#:写使能——控制写时序;

VDD:接5V电源;

VSS:接地。

在对Flash进行编程操作前,必须保证存储单元为空。如果不为空,就必须先对Flash芯片进行擦除操作。由于Flash采用了模块分区的阵列结构,使得各个存储模块既可以整个芯片一齐被擦除,还可以使各个存储模块被独立的分别擦除。只需在地址和数据端写入不同的操作命令即可实现不同的擦除操作。

SST39SF010的编程操作分三步骤:第一步是连续载入三字节命令的软件数据保护操作,第二步是写入字节地址和字节数据,在编程操作过程中,地址是在CE#或WE#的下降沿时有效,而数据则是在CE#或WE#的上升沿时有效;第三步是芯片内部的编程操作,该操作在CE#或WE#的第四个上升沿有效,随后该内部编程操作在30微秒内即可完成。

FLASH的编程操作是自动字节操作,编程时要特别注意编程时间参数和使用的命令集。编程和擦除时钟周期的定时参数如表所示。

3 FPGA实现Flash编程器的设计

Flash编程器的关键是要保证Flash地址和数据信号在时序上的严格要求,由SST39SF010的编程和擦除周期时序参数得知,它的地址或数据信号的建立和保持时间的最小时钟周期仅为30ns。为此,我们采用了40MHz的晶振作为FPGA的驱动时钟,它的最小时钟周期为25ns,完全可满足最小的时间周期要求。

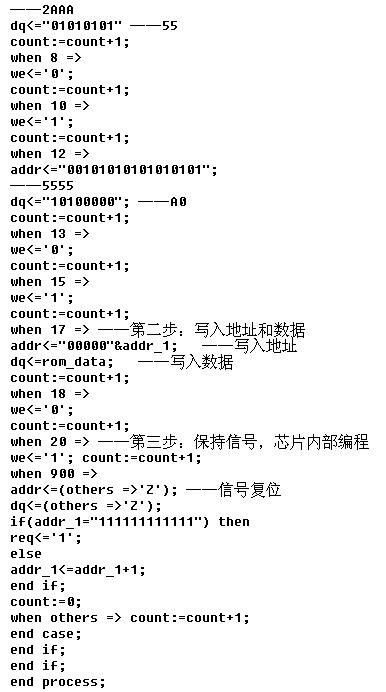

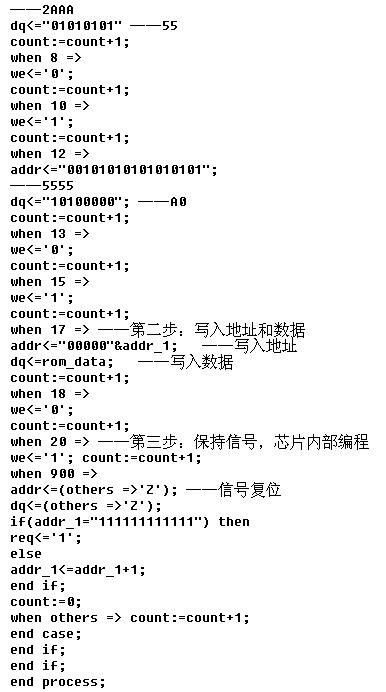

采用FPGA来实现Flash编程器,主要是如何对Flash进行写操作,利用VHDL语言编写的写操作进程表示如下:

实现一个控制功能,可以用有限状态机实现,也可以用CPU实现,二者相比,前者性能远高于后者。因为,在Von Neumann结构的CPU中,需要许多操作(例如取数和执行)和部件(例如数据通路和ALU寄存器)。而状态机中,状态存储在多个触发器中,表示行为的代码存储在门级网络中。对于通常的一条选择判断语句,如果用CPU实现,一般需要10~20条机器指令,其执行时间与CPU的速度有关。如果由门和触发器实现,则执行时间为一个时钟周期。因此用VHDL实现的状态机的控制性能要优于CPU实现的方案。

如上述程序,在编程器的写操作进程中,我们使用Moore型状态机,它最大的特点是输出仅是状态向量的函数,即Moore状态机的输出仅和当前状态(现态)有关。在寄存器转移级的有限状态机中包括状态进程和组合进程两部分。

状态进程:状态进程对状态机的时钟信号敏感,当时钟发生有效跳变时,状态机的状态发生变化,由次态变为现态。本例中,将写操作分成900个状态,状态0初始化各输出信号,状态1~5执行第一个控制命令,状态7—10执行如第二个控制命令,状态12~15执行第三个控制命令,状态17~ 20给出要写入的地址和数据,状态21~900保持控制信号,是芯片内部编程时间。 组合进程:组合进程就根据当前状态(现态)给输出信号赋值,并决定下一状态(次态)。在本例中,状态机根据不同的状态对CE#、OE#、 WE、地址、数据等Flash控制信号进行赋值,从而实现对Flash的控制功能。

但是每执行一次写操作,只能写入一个地址单元里的8bit数据,如果按照这个方法,完成整个Flash芯片1Mbit数据的写入就需要重复执行写操作 128K次,这样既麻烦又浪费时间。我们选用的Xilinx公司SpartanⅡ系列FPGA,提供片上双端口同步读/写RAM块,每块RAM容量为4096bit。块RAM的每个端口可独立配置为读/写端口、读端口或写端口,同时还能配置为任何想要的数据带宽。因此块RAM可使FPGA设计者的设计更加简单,可以把块RAM配置成ROM、RAM、FIFO等多种元件,具有使用方便、性能优越等特点,是一种十分高效的内部存储器解决方案。因此我们采用FPGA的块RAM作为内部数据缓冲器,以提高 Flash写操作的速度和效率。

在本例中,使用内部块RAM产生一个32Kbit 的ROM 元件,程序当中直接引用和映射该元件,将要写入Flash的数据先写入该ROM元件中,然后在每次写操作中将ROM中的数据按地址顺序逐一写入Flash中的一个连续32Kbit的扇区当中,这样编程器的一次写操作就可以写入32Kbit数据,因为32K×32=1Mbit,则依次改变Flash的高5位地址,重复32次上述的写操作,这样1Mbit的数据就写入了整片Flash中,大大提高了编程器写操作的效率。至于ROM元件中的数据,则以ASCⅡ码的形式存在以.co e为后缀的文件当中,在由 CoreGenerator生成ROM元件时,根据需要选择相应存有数据的.coe文件,将该文件的路径导入,执行Generate操作,最后生成的ROM元件就包含了.coe文件中的数据。

CoeGenerator是一个元件生成软件,它给用户提供了一个通用化的设计界面,提供RAM、ROM、乘法器、各种标准接口等许多设计中常用的元件模型,这样设计者不必自己动手编写,而采用CoeGenerator即可生成自己需要的各种元件。这些元件都是经过了最优化设计,占用资源最少,性能最优,还大大节省了设计时间,方便了设计者。产生的ROM元件将存储在设计工程之中,需要在程序中加入引用语句,才可以使用。 VHDL程序中使用CoreGenerator产生的元件需要加入两段语句,一是在实体部分对要引用的ROM元件进行说明,二是在结构体中对ROM元件例化,映射例化元件的输入/输出信号。 由于FPGA具有在线可再编程性能,因此当系统中FLASH 直接由FPGA存取时,我们可以用FPGA实现对Flash的编程,在编程操作之后,对FPGA 进行再配置,实现其它系统功能,达到一个FPGA器件实现多种应用的目的。

闪速存储器(FLASH Memory)以其集成度高、成本低、使用方便等许多优点,广泛应用于通讯设备、办公设备、家用电器、医疗设备等领域。利用其保存信息的非易失性和在线更新数据参数的特性,可将其作为具有一定灵活性的只读存储器(ROM)使用。

现在的数字电路应用系统设计中,经常遇到大容量的数据存储问题。Flash由于容量大、存储速度快、体积小、功耗低等诸多优点,而成为应用系统中数据存储器件的首选。由于在研制实时信号处理系统时,需要一块大容量的Flash来存储坐标变换的数据作查找表,因此面临一个如何对Flash进行编程,将数据写入Flash的问题。由于我们选用的Flash芯片为SST39SF010/020,是最新生产的型号,需要自己开发编程器来满足设计需要,达到既经济又实用的目的。这一型号的Flash采用的是标准的5V电压供电,器件在命令控制下自己产生内部的擦除电压Vpp,从而完成数据的写入和芯片的擦除等各种功能。而FPGA这种大规模的可编程器件十分适合逻辑电路的设计,能方便地控制和产生 Flash编程操作中的各种控制命令,实现编程器的功能。

2 Flash的性能参数和操作时序

以最新的Flash芯片型号SST39SF010/020为例,容量为1/2Mbit(×8)。 它的主要性能有:

● 单一的5.0V电压读写操作;

● 高可靠性,超过100年的数据保持能力;

● 快速擦除和字节编程功能

——扇区擦除时间典型值只需7ms;

——片擦除时间典型值只需15ms;

——字节编程需时间典型值只需20微秒;

——片重写时间需3ms(SST39SF010)

● 片内部产生Vpp编程电压,实现自动读写时序;

● I/O兼容TTL;

各引脚功能:

Ams~A0:地址输入 ——提供存储器地址;

DQ7~DQ0:数据输入/输出 ——在读时序时输出数据,在写时序时接收输入的数据;

CE#:片选使能——当CE#为低电平有效;

OE#:输出使能——选通输出缓存器;

WE#:写使能——控制写时序;

VDD:接5V电源;

VSS:接地。

在对Flash进行编程操作前,必须保证存储单元为空。如果不为空,就必须先对Flash芯片进行擦除操作。由于Flash采用了模块分区的阵列结构,使得各个存储模块既可以整个芯片一齐被擦除,还可以使各个存储模块被独立的分别擦除。只需在地址和数据端写入不同的操作命令即可实现不同的擦除操作。

SST39SF010的编程操作分三步骤:第一步是连续载入三字节命令的软件数据保护操作,第二步是写入字节地址和字节数据,在编程操作过程中,地址是在CE#或WE#的下降沿时有效,而数据则是在CE#或WE#的上升沿时有效;第三步是芯片内部的编程操作,该操作在CE#或WE#的第四个上升沿有效,随后该内部编程操作在30微秒内即可完成。

FLASH的编程操作是自动字节操作,编程时要特别注意编程时间参数和使用的命令集。编程和擦除时钟周期的定时参数如表所示。

3 FPGA实现Flash编程器的设计

Flash编程器的关键是要保证Flash地址和数据信号在时序上的严格要求,由SST39SF010的编程和擦除周期时序参数得知,它的地址或数据信号的建立和保持时间的最小时钟周期仅为30ns。为此,我们采用了40MHz的晶振作为FPGA的驱动时钟,它的最小时钟周期为25ns,完全可满足最小的时间周期要求。

采用FPGA来实现Flash编程器,主要是如何对Flash进行写操作,利用VHDL语言编写的写操作进程表示如下:

实现一个控制功能,可以用有限状态机实现,也可以用CPU实现,二者相比,前者性能远高于后者。因为,在Von Neumann结构的CPU中,需要许多操作(例如取数和执行)和部件(例如数据通路和ALU寄存器)。而状态机中,状态存储在多个触发器中,表示行为的代码存储在门级网络中。对于通常的一条选择判断语句,如果用CPU实现,一般需要10~20条机器指令,其执行时间与CPU的速度有关。如果由门和触发器实现,则执行时间为一个时钟周期。因此用VHDL实现的状态机的控制性能要优于CPU实现的方案。

如上述程序,在编程器的写操作进程中,我们使用Moore型状态机,它最大的特点是输出仅是状态向量的函数,即Moore状态机的输出仅和当前状态(现态)有关。在寄存器转移级的有限状态机中包括状态进程和组合进程两部分。

状态进程:状态进程对状态机的时钟信号敏感,当时钟发生有效跳变时,状态机的状态发生变化,由次态变为现态。本例中,将写操作分成900个状态,状态0初始化各输出信号,状态1~5执行第一个控制命令,状态7—10执行如第二个控制命令,状态12~15执行第三个控制命令,状态17~ 20给出要写入的地址和数据,状态21~900保持控制信号,是芯片内部编程时间。 组合进程:组合进程就根据当前状态(现态)给输出信号赋值,并决定下一状态(次态)。在本例中,状态机根据不同的状态对CE#、OE#、 WE、地址、数据等Flash控制信号进行赋值,从而实现对Flash的控制功能。

但是每执行一次写操作,只能写入一个地址单元里的8bit数据,如果按照这个方法,完成整个Flash芯片1Mbit数据的写入就需要重复执行写操作 128K次,这样既麻烦又浪费时间。我们选用的Xilinx公司SpartanⅡ系列FPGA,提供片上双端口同步读/写RAM块,每块RAM容量为4096bit。块RAM的每个端口可独立配置为读/写端口、读端口或写端口,同时还能配置为任何想要的数据带宽。因此块RAM可使FPGA设计者的设计更加简单,可以把块RAM配置成ROM、RAM、FIFO等多种元件,具有使用方便、性能优越等特点,是一种十分高效的内部存储器解决方案。因此我们采用FPGA的块RAM作为内部数据缓冲器,以提高 Flash写操作的速度和效率。

在本例中,使用内部块RAM产生一个32Kbit 的ROM 元件,程序当中直接引用和映射该元件,将要写入Flash的数据先写入该ROM元件中,然后在每次写操作中将ROM中的数据按地址顺序逐一写入Flash中的一个连续32Kbit的扇区当中,这样编程器的一次写操作就可以写入32Kbit数据,因为32K×32=1Mbit,则依次改变Flash的高5位地址,重复32次上述的写操作,这样1Mbit的数据就写入了整片Flash中,大大提高了编程器写操作的效率。至于ROM元件中的数据,则以ASCⅡ码的形式存在以.co e为后缀的文件当中,在由 CoreGenerator生成ROM元件时,根据需要选择相应存有数据的.coe文件,将该文件的路径导入,执行Generate操作,最后生成的ROM元件就包含了.coe文件中的数据。

CoeGenerator是一个元件生成软件,它给用户提供了一个通用化的设计界面,提供RAM、ROM、乘法器、各种标准接口等许多设计中常用的元件模型,这样设计者不必自己动手编写,而采用CoeGenerator即可生成自己需要的各种元件。这些元件都是经过了最优化设计,占用资源最少,性能最优,还大大节省了设计时间,方便了设计者。产生的ROM元件将存储在设计工程之中,需要在程序中加入引用语句,才可以使用。 VHDL程序中使用CoreGenerator产生的元件需要加入两段语句,一是在实体部分对要引用的ROM元件进行说明,二是在结构体中对ROM元件例化,映射例化元件的输入/输出信号。 由于FPGA具有在线可再编程性能,因此当系统中FLASH 直接由FPGA存取时,我们可以用FPGA实现对Flash的编程,在编程操作之后,对FPGA 进行再配置,实现其它系统功能,达到一个FPGA器件实现多种应用的目的。

电路 电压 FPGA VHDL Xilinx 电子 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)