微机保护控制接口装置的CPLD抗干扰设计

时间:08-02

来源:互联网

点击:

微机保护装置控制接口设计

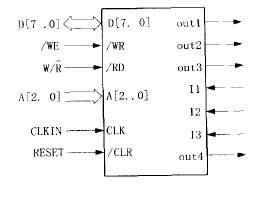

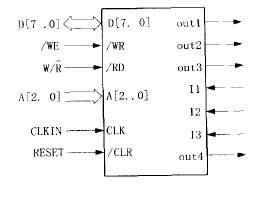

微机保护系统的控制接口由I/O接口和微型继电器组成,典型电路是将分合闸继电器分成2级,第1级控制第2级。第2级控制主回路的分合闸接触器。原理框图如图1所示。

2级继电器有利于隔离主回路的分合闸接触器通断产生的干扰。

合闸指令执行顺序为:OUT1→OUT2→OUT4。分闸指令执行顺序为:OUT1→OUT3→OUT4。如果I/O接口直接由CPU控制,当CPU受干扰程序跑飞或CPU芯片出故障使I/O接口失控,正巧产生分合闸所需的电平时,继电保护控制出口就不可避免地发生误动。

图1继电保护控制出口原理

因此,继电保护控制出口的闭锁和冗余度设计是防止控制出口误动的关键所在。严格监视分合闸多重命令的执行顺序,不允许无序分合闸命令通过,是防止控制出口误动的根本措施。分合闸多重命令的有序执行,可以看作一个状态变化序列,用CPLD状态机对这个状态序列进行监控,就能杜绝无序状态的通过,实现控制出口的无干扰控制。

基于CPLD状态机的抗干扰控制接口设计

设计一个基于DSP的高压开关柜微机综合保护系统时,用一片CPLD芯片实现图1所示的I/O接口,并设计一个有限状态机,对状态输入I1,I2,I3进行监控,状态机输出作为总分合闸命令的允许和禁止信号。基于CPLD的微机保护控制接口如图2 所示。

图2微机保护的CPLD控制接口

分合闸多重命令的状态编码

状态机有3位二进制输入,共有23=8种状态。采用二进制编码方式(Binary coded)将控制接口的初始状态S0到所有可能的状态变迁,列成一张编码表,如表1 所示。状态编码表是编写VHDL程序的基础。

表1微机保护控制接口状态机编码表

状态机设计

状态机的时钟频率为5MHz。复位信号/Reset来自DSP微机保护装置的系统复位信号,对状态机的状态初始化。

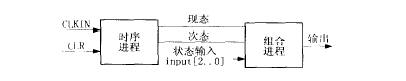

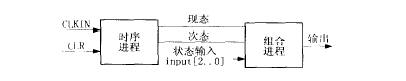

状态机的设计可采用单进程,双进程,3进程等进行编写,根据微机保护控制接口的应用特点宜采用双进程来描述状态机,即一个时序进程和一个组合进程。时序进程负责旧次态到新现态的转换,以及异步复位。组合进程完成根据现态决定状态机输出的变化,根据状态输入来决定新的次态。双进程状态机的逻辑框图如图3所示。

图3双进程状态机逻辑图

状态机的行为及代码是一种流程控制代码,很容易用VHDL语言中的CASE语句和IF语句加以实现。时序进程与组合进程之间利用现态信号和次态信号进行同步通信。

状态机仿真波形

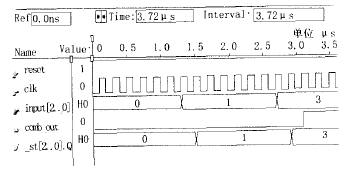

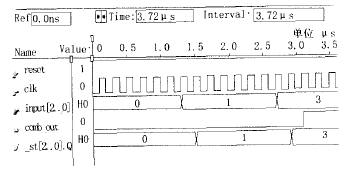

利用Altera公司的EDA工具软件MAX+plus对用VHDL语言设计的状态机进行时序仿真,仿真波形如图4所示。

图4状态机仿真波形

CPLD状态机抗干扰控制原理分析

基于CPU的微机系统是按指令周期顺序执行机器指令的,一旦受干扰程序出轨,则CPU不按事先编好的流程执行程序,出现死机,通常的对策是设置看门狗使CPU硬件复位,使CPU重新运行正常程序,但是从CPU死机到看门狗复位一般要经历几毫秒到1~2s,这段失控时间,继电保护控制出口的状态是不可预测的,足以对继电保护系统构成危害,严重情况就是发生误动。而基于CPLD的状态机系统,状态变换周期只有一个时钟周期,若时钟频率为5MHz,时钟周期为012Ls。若状态机受干扰进入非法状态再转入合法状态,只需2个时钟周期,即几百纳秒,不足以对状态机系统运行造成危害。可见,用CPLD状态机控制微机继电保护的控制接口,就能实现无干扰控制,获得继电保护系统的高可靠性控制。

就DSP芯片与CPLD芯片的可靠性比较而言,DSP的外围接口繁多,输入信号有模拟和数字,电压有模拟电压和数字电压,CPLD只有数字接口,电压单一,受外界干扰损坏的可能性比DSP小的多。另外,CPLD状态机含有多个进程,就相当于包含有并行运算的“多CPU”功能,对不合格的输入,裁决状态机输出0。因此,笔者认为,双CPU控制硬件冗余设计远不如CPLD状态机的控制接口可靠性高。

结论

用Altera公司的MAX7000系列的EMp7128SLC84-15实现继电保护控制接口,与TMS320F240DSP芯片总线直接相连,DSP执行合闸或分闸多重命令时,不需要插入等待周期,只需要连续执行3条合闸或分闸指令,CPLD状态机就能立即决定是否允许总执行命令通过。试验表明: 用CPLD实现的继电保护控制接口具有速度快,占用硬件体积小,接口简单,可靠性高等特点。

该接口应用到基于TMS320F240的高压开关柜数字综合保护装置中,随KJ118型矿用变电所远程监控系统于2003年10月在徐州矿务局旗山煤矿井下采区变电所投运,进行工业性试验,正常运行至今已超过半年以上。采区变电所现场高爆开关就地人工分合闸操作、地面主机遥控命令分合闸以及故障保护跳闸试验表明,从未发生因高压开关分合闸操作等强电磁干扰引起CPU程序出轨而误动,表现出非常高的可靠性。

文中用全新的CPLD状态机方法研究微机保护系统的控制可靠性问题,对于瞬变干扰信号有很强的滤波性。虽然从防范微机保护系统程序出轨采用一些软件措施有一定效果,但是并不能真正解决程序出轨期间控制口的失控问题,而文中提出的CPLD状态机控制接口真正解决了这一问题,可以推广到各种微机控制系统的抗干扰控制接口设计中去。

微机保护系统的控制接口由I/O接口和微型继电器组成,典型电路是将分合闸继电器分成2级,第1级控制第2级。第2级控制主回路的分合闸接触器。原理框图如图1所示。

2级继电器有利于隔离主回路的分合闸接触器通断产生的干扰。

合闸指令执行顺序为:OUT1→OUT2→OUT4。分闸指令执行顺序为:OUT1→OUT3→OUT4。如果I/O接口直接由CPU控制,当CPU受干扰程序跑飞或CPU芯片出故障使I/O接口失控,正巧产生分合闸所需的电平时,继电保护控制出口就不可避免地发生误动。

图1继电保护控制出口原理

因此,继电保护控制出口的闭锁和冗余度设计是防止控制出口误动的关键所在。严格监视分合闸多重命令的执行顺序,不允许无序分合闸命令通过,是防止控制出口误动的根本措施。分合闸多重命令的有序执行,可以看作一个状态变化序列,用CPLD状态机对这个状态序列进行监控,就能杜绝无序状态的通过,实现控制出口的无干扰控制。

基于CPLD状态机的抗干扰控制接口设计

设计一个基于DSP的高压开关柜微机综合保护系统时,用一片CPLD芯片实现图1所示的I/O接口,并设计一个有限状态机,对状态输入I1,I2,I3进行监控,状态机输出作为总分合闸命令的允许和禁止信号。基于CPLD的微机保护控制接口如图2 所示。

图2微机保护的CPLD控制接口

分合闸多重命令的状态编码

状态机有3位二进制输入,共有23=8种状态。采用二进制编码方式(Binary coded)将控制接口的初始状态S0到所有可能的状态变迁,列成一张编码表,如表1 所示。状态编码表是编写VHDL程序的基础。

表1微机保护控制接口状态机编码表

状态机设计

状态机的时钟频率为5MHz。复位信号/Reset来自DSP微机保护装置的系统复位信号,对状态机的状态初始化。

状态机的设计可采用单进程,双进程,3进程等进行编写,根据微机保护控制接口的应用特点宜采用双进程来描述状态机,即一个时序进程和一个组合进程。时序进程负责旧次态到新现态的转换,以及异步复位。组合进程完成根据现态决定状态机输出的变化,根据状态输入来决定新的次态。双进程状态机的逻辑框图如图3所示。

图3双进程状态机逻辑图

状态机的行为及代码是一种流程控制代码,很容易用VHDL语言中的CASE语句和IF语句加以实现。时序进程与组合进程之间利用现态信号和次态信号进行同步通信。

状态机仿真波形

利用Altera公司的EDA工具软件MAX+plus对用VHDL语言设计的状态机进行时序仿真,仿真波形如图4所示。

图4状态机仿真波形

CPLD状态机抗干扰控制原理分析

基于CPU的微机系统是按指令周期顺序执行机器指令的,一旦受干扰程序出轨,则CPU不按事先编好的流程执行程序,出现死机,通常的对策是设置看门狗使CPU硬件复位,使CPU重新运行正常程序,但是从CPU死机到看门狗复位一般要经历几毫秒到1~2s,这段失控时间,继电保护控制出口的状态是不可预测的,足以对继电保护系统构成危害,严重情况就是发生误动。而基于CPLD的状态机系统,状态变换周期只有一个时钟周期,若时钟频率为5MHz,时钟周期为012Ls。若状态机受干扰进入非法状态再转入合法状态,只需2个时钟周期,即几百纳秒,不足以对状态机系统运行造成危害。可见,用CPLD状态机控制微机继电保护的控制接口,就能实现无干扰控制,获得继电保护系统的高可靠性控制。

就DSP芯片与CPLD芯片的可靠性比较而言,DSP的外围接口繁多,输入信号有模拟和数字,电压有模拟电压和数字电压,CPLD只有数字接口,电压单一,受外界干扰损坏的可能性比DSP小的多。另外,CPLD状态机含有多个进程,就相当于包含有并行运算的“多CPU”功能,对不合格的输入,裁决状态机输出0。因此,笔者认为,双CPU控制硬件冗余设计远不如CPLD状态机的控制接口可靠性高。

结论

用Altera公司的MAX7000系列的EMp7128SLC84-15实现继电保护控制接口,与TMS320F240DSP芯片总线直接相连,DSP执行合闸或分闸多重命令时,不需要插入等待周期,只需要连续执行3条合闸或分闸指令,CPLD状态机就能立即决定是否允许总执行命令通过。试验表明: 用CPLD实现的继电保护控制接口具有速度快,占用硬件体积小,接口简单,可靠性高等特点。

该接口应用到基于TMS320F240的高压开关柜数字综合保护装置中,随KJ118型矿用变电所远程监控系统于2003年10月在徐州矿务局旗山煤矿井下采区变电所投运,进行工业性试验,正常运行至今已超过半年以上。采区变电所现场高爆开关就地人工分合闸操作、地面主机遥控命令分合闸以及故障保护跳闸试验表明,从未发生因高压开关分合闸操作等强电磁干扰引起CPU程序出轨而误动,表现出非常高的可靠性。

文中用全新的CPLD状态机方法研究微机保护系统的控制可靠性问题,对于瞬变干扰信号有很强的滤波性。虽然从防范微机保护系统程序出轨采用一些软件措施有一定效果,但是并不能真正解决程序出轨期间控制口的失控问题,而文中提出的CPLD状态机控制接口真正解决了这一问题,可以推广到各种微机控制系统的抗干扰控制接口设计中去。

变压器 电压 电动机 EMC 单片机 电路 滤波器 看门狗 CPLD FPGA VHDL 继电器 DSP 仿真 Altera EDA 总线 相关文章:

- 基于CPLD的CCD信号发生器的研究(04-08)

- 现场可编程门阵列的供电(03-24)

- FPGA控制CLC5958型A/D转换器高速PCI采集(06-08)

- 基于MCU+CPLD变压器测试系统的设计与实现(07-21)

- CPLD与绝对式编码器在高精度高速伺服单元中的应用(07-28)

- 基于FPGA的IRIG-B编码器的设计(08-20)