现场可编程门阵列的供电

时间:03-24

来源:互联网

点击:

FPGA概述

现场可编程门阵列(FPGA)是一种可编程逻辑器件,由成千上万个完全相同的可编程逻辑单元组成,周围是输入/输出单元构成的外设。制造完成后,FPGA可以在工作现场编程,以便实现特定的设计功能。典型设计工作包括指定各单元的简单逻辑功能,并选择性地闭合互连矩阵中的一些开关。为确保正常工作,FPGA必须运用适当的电源管理技术。FPGA最初用于系统原型制作,最终量产时会用高速IC或 ASIC代替。不过,近年来FPGA的性能有很大改善,成本则不断下降,因此FPGA现已广泛用于生产设计。

FPGA的功耗取决于许多不同因素,与设计密切相关。必须运用精确的功耗估算方法,才能确保电源系统符合FPGA要求。FPGA制造商会提供网络工具,用于功耗计算。为了估算 FPGA的功耗,计算程序需考虑设计资源运用、切换速率、工作时钟频率、I/O使用及其它许多因素。

FPGA主要有三种可配置元件:可配置逻辑模块(CLB)、I/O模块(IOB)和互连。其中,CLB提供功能逻辑元件,IOB提供封装引脚与内部信号线之间的接口,可编程互连资源提供路由路径,将CLB和IOB的输入和输出与适合的网络相连。CLB(或内核)上施加的电压称为VCCINT。VCCO是IOB的电源电压。一些FPGA还有其它电压输入,称为VCCAUX。VCCINT(用于CLB)的典型值为1.0V、1.2V、1.5V、1.8V、2.5V和3V,电流可达10A或更高。 CLB数量越多,则电压越低,电流越高。启动时,VCCINT必须单调上升,不得下跌。最常用的VCCO电压(用于IOB)为1.2V、1.5V、 1.8V、2.5V、3.3V或传统系统中的5V。电流范围为1A至20A。辅助电压(VCCAUX)典型值为3.3V或2.5V。它为FPGA中的时间关键资源供电,因此易受电源噪声影响。VCCAUX可以与VCCO共用一个电源层,但前提是VCCO不会产生过大的噪声。

FPGA使用的电源类型

FPGA电源要求输出电压范围从1.2V到5V,输出电流范围从数十毫安到数安培。可用三种电源:低压差(LDO)线性稳压器、开关式DC-DC稳压器和开关式电源模块。最终选择何种电源取决于系统、系统预算和上市时间要求。

如果电路板空间是首要考虑因素,低输出噪声十分重要,或者系统要求对输入电压变化和负载瞬变做出快速响应,则应使用LDO稳压器。LDO功效比较低(因为是线性稳压器),只能提供中低输出电流。输入电容通常可以降低LDO输入端的电感和噪声。LDO输出端也需要电容,用来处理系统瞬变,并保持系统稳定性。也可以使用双输出LDO,同时为 VCCINT和VCCO供电。

如果在设计中效率至关重要,并且系统要求高输出电流,则开关式稳压器占优势。开关电源的功效比高于LDO,但其开关电路会增加输出噪声。与LDO不同,开关式稳压器需利用电感来实现DC-DC转换。

FPGA的特殊电源要求

为确保正确上电,内核电压VCCINT的缓升时间必须在制造商规定的范围内。对于一些FPGA,由于VCCINT会在晶体管阈值导通前停留更多时间,因此过长的缓升时间可能会导致启动电流持续较长时间。如果电源向FPGA提供大电流,则较长的上电缓升时间会引起热应力。ADI公司的DC-DC稳压器提供可调软启动,缓升时间可以通过外部电容进行控制。缓升时间典型值在20ms至100ms范围内。

许多FPGA没有时序控制要求,因此 VCCINT、VCCO和VCCAUX可以同时上电。如果这一点无法实现,上电电流可以稍高。时序要求依具体FPGA而异。对于一些FPGA,必须同时给 VCCINT和VCCO供电。对于另一些FPGA,这些电源可按任何顺序接通。多数情况下,先给VCCINT后给VCCO供电是一种较好的做法。

当 VCCINT在0.6V至0.8V范围内时,某些FPGA系列会产生上电涌入电流。在此期间,电源转换器持续供电。这种应用中,因为器件需通过降低输出电压来限制电流,所以不推荐使用返送电流限制。但在限流电源解决方案中,一旦限流电源所供电的电路电流超过设定的额定电流,电源就会将该电流限制在额定值以下。

FPGA配电结构

对于高速、高密度FPGA器件,保持良好的信号完整性对于实现可靠、可重复的设计十分关键。适当的电源旁路和去耦可以改善整体信号完整性。如果去耦不充分,逻辑转换将会影响电源和地电压,导致器件工作不正常。此外,采用分布式电源结构也是一种主要解决方案,给FPGA供电时可以将电源电压偏移降至最低。

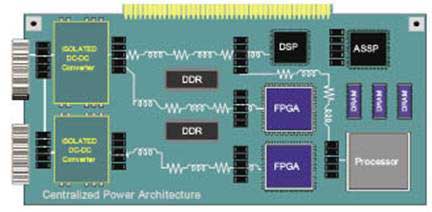

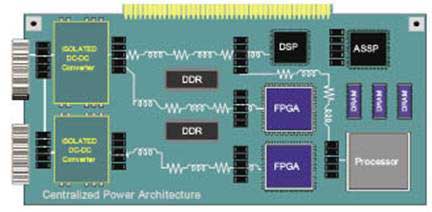

在传统电源结构中,AC/DC或DC/DC转换器位于一个地方,并提供多个输出电压,在整个系统内分配。这种设计称为集中式电源结构(CPA),见图1。以高电流分配低电压时,铜线或PCB轨道会产生严重的电阻损耗,CPA就会发生问题。

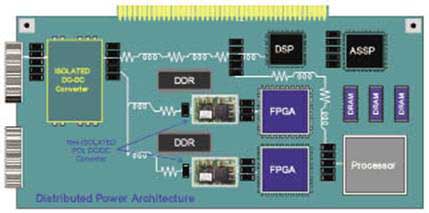

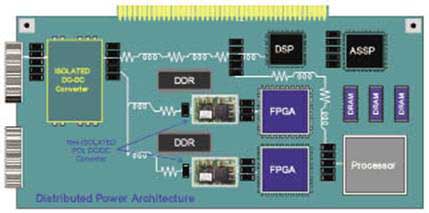

CPA的替代方案是分布式电源结构(DPA),见图2。采用DPA时,整个系统内仅分配一个半稳压的DC电压,各DC/DC转换器(线性或开关式)与各负载相邻。DPA中,DC/DC转换器与负载(例如FPGA)之间的距离近得多,因而线路电阻和配线电感引起的电压下降得以减小。这种为负载提供本地电源的方法称为负载点(POL)。

图1 集中式电源结构

图2 分布式电源结构

当一个逻辑器件从逻辑1切换到逻辑0时,或者从逻辑 0切换到逻辑1时,包括电源的输出结构暂时变为低阻抗状态。每次转换均要求对信号线进行充电或放电,这就需要能量。旁路电容的功能是在本地储存能量,以提供转换所需的能量。

本地储存能量必须在较宽的频率范围内可用。低串联电感的非常小的电容用来为高频转换提供快速电流。高频电容能量耗尽之后,较大、较慢的电容继续提供电流。FPGA技术要求三种频率范围内的电容,即高、中、低频率范围。这些频率的跨度为1kHz至500MHz。

正确放置对于高频电容(1nF至100nF低电感陶瓷片式电容)非常重要;对于中频电容(10μF至100μF钽电容或陶瓷电容)和低频电容 (>470μF),这种重要性依次降低。之所以与放置有关,原因很简单:从电容引脚到FPGA电源引脚的路径电感必须尽可能低。这意味着该路径必须尽可能短,哪怕要穿过实体接地层或电源层。1英寸实心铜层的电感约为1nH,因此距离极为重要。旁路电容过孔必须直接下行至接地层或VCC层。

高频旁路电容,无论是在VCCINT还是VCCIO上,均应安装在相关VCC引脚的1厘米范围内;中频旁路电容则应安装在VCC引脚的3厘米范围内。低频旁路电容可以安装在合理范围内的电路板上任意位置。当然,离FPGA越近越好。

较新的FPGA有输入/输出旁路要求,因此以前用于低速或低密度设计的电容类型可能无效。根据所用材料、结构和值的不同,旁路电容在整个频率范围内有不同的串联电抗。通过查看各种系列的数据手册,可以得知某些电容更适合当前所考虑的应用。

图3中显示了电容阻抗随频率的变化曲线。阻抗最小值位于电容的自谐振频率;超过此频率后,寄生引线电感在“电容”的电抗特性中占据主导地位。图中,业界标准型X7R单芯片、10nF陶瓷1206片式电容在50MHz时的阻抗为0.2Ω。然而,在500MHz时,该电容的阻抗约为3Ω。当有效阻抗增大,负载无法使用电容所储存的能量时,电容即无效。同时还必须考虑温度范围和老化效应。一些电容在室温时阻抗较低,但在极端温度时则表现不佳。当电容值较大(100nF至330nF)时,Z5U电容在高频时的ESR可能较低。不过,这种电容不宜在10℃以下使用。作为+20%、–80%额定器件,这种电容要求几乎两倍的设计值才能安全使用。选择旁路电容系列时,最好查看电容制造商的数据手册。

FPGA 电源设计可能会涉及5A、10A甚至更高的电流在PCB走线中流动。当这种大电流存在并以开关模式(边沿陡峭)随时间变化时,显而易见,噪声、感应电压和电磁辐射(EMI)很可能出现,并可能导致电源工作异常。与配线电感相关的快速开关电流也可能会产生电压瞬变,并导致其它问题。为使电感和接地环路最小,传导高电流的PCB走线应尽可能短。应采用接地层结构或单点接地,使外部元件尽可能靠近DC/DC转换器,以实现最佳效果。使用开口铁芯电感时,必须特别注意这种电感的位置和定位,避免电感通量与敏感的反馈接地路径和COUT配线相交。使用具有可调输出的开关稳压器或控制器时,应将反馈电阻和相关配线置于 IC附近,并远离电感布置配线,尤其是开口铁芯式电感。铁氧体绕轴或铁棒电感具有从绕轴一端经空气到达另一端的磁力线。这些磁力线会在电感磁场范围内的所有导线或PC板铜走线中产生感应电压。铜走线中产生的电压量由以下因素决定:磁场强度、PC铜走线相对于磁场的方向和位置,以及铜走线与电感之间的距离。

FPGA 和稳压器的可靠性取决于散热问题。这些器件的温度主要受待机功耗和总功耗、外部容性负载(仅FPGA)、热阻、环境温度以及气流等因素控制。必须有效管理这些因素,使结温(Tj)始终低于制造商规定的最高温度。

现场可编程门阵列(FPGA)是一种可编程逻辑器件,由成千上万个完全相同的可编程逻辑单元组成,周围是输入/输出单元构成的外设。制造完成后,FPGA可以在工作现场编程,以便实现特定的设计功能。典型设计工作包括指定各单元的简单逻辑功能,并选择性地闭合互连矩阵中的一些开关。为确保正常工作,FPGA必须运用适当的电源管理技术。FPGA最初用于系统原型制作,最终量产时会用高速IC或 ASIC代替。不过,近年来FPGA的性能有很大改善,成本则不断下降,因此FPGA现已广泛用于生产设计。

FPGA的功耗取决于许多不同因素,与设计密切相关。必须运用精确的功耗估算方法,才能确保电源系统符合FPGA要求。FPGA制造商会提供网络工具,用于功耗计算。为了估算 FPGA的功耗,计算程序需考虑设计资源运用、切换速率、工作时钟频率、I/O使用及其它许多因素。

FPGA主要有三种可配置元件:可配置逻辑模块(CLB)、I/O模块(IOB)和互连。其中,CLB提供功能逻辑元件,IOB提供封装引脚与内部信号线之间的接口,可编程互连资源提供路由路径,将CLB和IOB的输入和输出与适合的网络相连。CLB(或内核)上施加的电压称为VCCINT。VCCO是IOB的电源电压。一些FPGA还有其它电压输入,称为VCCAUX。VCCINT(用于CLB)的典型值为1.0V、1.2V、1.5V、1.8V、2.5V和3V,电流可达10A或更高。 CLB数量越多,则电压越低,电流越高。启动时,VCCINT必须单调上升,不得下跌。最常用的VCCO电压(用于IOB)为1.2V、1.5V、 1.8V、2.5V、3.3V或传统系统中的5V。电流范围为1A至20A。辅助电压(VCCAUX)典型值为3.3V或2.5V。它为FPGA中的时间关键资源供电,因此易受电源噪声影响。VCCAUX可以与VCCO共用一个电源层,但前提是VCCO不会产生过大的噪声。

FPGA使用的电源类型

FPGA电源要求输出电压范围从1.2V到5V,输出电流范围从数十毫安到数安培。可用三种电源:低压差(LDO)线性稳压器、开关式DC-DC稳压器和开关式电源模块。最终选择何种电源取决于系统、系统预算和上市时间要求。

如果电路板空间是首要考虑因素,低输出噪声十分重要,或者系统要求对输入电压变化和负载瞬变做出快速响应,则应使用LDO稳压器。LDO功效比较低(因为是线性稳压器),只能提供中低输出电流。输入电容通常可以降低LDO输入端的电感和噪声。LDO输出端也需要电容,用来处理系统瞬变,并保持系统稳定性。也可以使用双输出LDO,同时为 VCCINT和VCCO供电。

如果在设计中效率至关重要,并且系统要求高输出电流,则开关式稳压器占优势。开关电源的功效比高于LDO,但其开关电路会增加输出噪声。与LDO不同,开关式稳压器需利用电感来实现DC-DC转换。

FPGA的特殊电源要求

为确保正确上电,内核电压VCCINT的缓升时间必须在制造商规定的范围内。对于一些FPGA,由于VCCINT会在晶体管阈值导通前停留更多时间,因此过长的缓升时间可能会导致启动电流持续较长时间。如果电源向FPGA提供大电流,则较长的上电缓升时间会引起热应力。ADI公司的DC-DC稳压器提供可调软启动,缓升时间可以通过外部电容进行控制。缓升时间典型值在20ms至100ms范围内。

许多FPGA没有时序控制要求,因此 VCCINT、VCCO和VCCAUX可以同时上电。如果这一点无法实现,上电电流可以稍高。时序要求依具体FPGA而异。对于一些FPGA,必须同时给 VCCINT和VCCO供电。对于另一些FPGA,这些电源可按任何顺序接通。多数情况下,先给VCCINT后给VCCO供电是一种较好的做法。

当 VCCINT在0.6V至0.8V范围内时,某些FPGA系列会产生上电涌入电流。在此期间,电源转换器持续供电。这种应用中,因为器件需通过降低输出电压来限制电流,所以不推荐使用返送电流限制。但在限流电源解决方案中,一旦限流电源所供电的电路电流超过设定的额定电流,电源就会将该电流限制在额定值以下。

FPGA配电结构

对于高速、高密度FPGA器件,保持良好的信号完整性对于实现可靠、可重复的设计十分关键。适当的电源旁路和去耦可以改善整体信号完整性。如果去耦不充分,逻辑转换将会影响电源和地电压,导致器件工作不正常。此外,采用分布式电源结构也是一种主要解决方案,给FPGA供电时可以将电源电压偏移降至最低。

在传统电源结构中,AC/DC或DC/DC转换器位于一个地方,并提供多个输出电压,在整个系统内分配。这种设计称为集中式电源结构(CPA),见图1。以高电流分配低电压时,铜线或PCB轨道会产生严重的电阻损耗,CPA就会发生问题。

CPA的替代方案是分布式电源结构(DPA),见图2。采用DPA时,整个系统内仅分配一个半稳压的DC电压,各DC/DC转换器(线性或开关式)与各负载相邻。DPA中,DC/DC转换器与负载(例如FPGA)之间的距离近得多,因而线路电阻和配线电感引起的电压下降得以减小。这种为负载提供本地电源的方法称为负载点(POL)。

图1 集中式电源结构

图2 分布式电源结构

当一个逻辑器件从逻辑1切换到逻辑0时,或者从逻辑 0切换到逻辑1时,包括电源的输出结构暂时变为低阻抗状态。每次转换均要求对信号线进行充电或放电,这就需要能量。旁路电容的功能是在本地储存能量,以提供转换所需的能量。

本地储存能量必须在较宽的频率范围内可用。低串联电感的非常小的电容用来为高频转换提供快速电流。高频电容能量耗尽之后,较大、较慢的电容继续提供电流。FPGA技术要求三种频率范围内的电容,即高、中、低频率范围。这些频率的跨度为1kHz至500MHz。

正确放置对于高频电容(1nF至100nF低电感陶瓷片式电容)非常重要;对于中频电容(10μF至100μF钽电容或陶瓷电容)和低频电容 (>470μF),这种重要性依次降低。之所以与放置有关,原因很简单:从电容引脚到FPGA电源引脚的路径电感必须尽可能低。这意味着该路径必须尽可能短,哪怕要穿过实体接地层或电源层。1英寸实心铜层的电感约为1nH,因此距离极为重要。旁路电容过孔必须直接下行至接地层或VCC层。

高频旁路电容,无论是在VCCINT还是VCCIO上,均应安装在相关VCC引脚的1厘米范围内;中频旁路电容则应安装在VCC引脚的3厘米范围内。低频旁路电容可以安装在合理范围内的电路板上任意位置。当然,离FPGA越近越好。

较新的FPGA有输入/输出旁路要求,因此以前用于低速或低密度设计的电容类型可能无效。根据所用材料、结构和值的不同,旁路电容在整个频率范围内有不同的串联电抗。通过查看各种系列的数据手册,可以得知某些电容更适合当前所考虑的应用。

图3中显示了电容阻抗随频率的变化曲线。阻抗最小值位于电容的自谐振频率;超过此频率后,寄生引线电感在“电容”的电抗特性中占据主导地位。图中,业界标准型X7R单芯片、10nF陶瓷1206片式电容在50MHz时的阻抗为0.2Ω。然而,在500MHz时,该电容的阻抗约为3Ω。当有效阻抗增大,负载无法使用电容所储存的能量时,电容即无效。同时还必须考虑温度范围和老化效应。一些电容在室温时阻抗较低,但在极端温度时则表现不佳。当电容值较大(100nF至330nF)时,Z5U电容在高频时的ESR可能较低。不过,这种电容不宜在10℃以下使用。作为+20%、–80%额定器件,这种电容要求几乎两倍的设计值才能安全使用。选择旁路电容系列时,最好查看电容制造商的数据手册。

FPGA 电源设计可能会涉及5A、10A甚至更高的电流在PCB走线中流动。当这种大电流存在并以开关模式(边沿陡峭)随时间变化时,显而易见,噪声、感应电压和电磁辐射(EMI)很可能出现,并可能导致电源工作异常。与配线电感相关的快速开关电流也可能会产生电压瞬变,并导致其它问题。为使电感和接地环路最小,传导高电流的PCB走线应尽可能短。应采用接地层结构或单点接地,使外部元件尽可能靠近DC/DC转换器,以实现最佳效果。使用开口铁芯电感时,必须特别注意这种电感的位置和定位,避免电感通量与敏感的反馈接地路径和COUT配线相交。使用具有可调输出的开关稳压器或控制器时,应将反馈电阻和相关配线置于 IC附近,并远离电感布置配线,尤其是开口铁芯式电感。铁氧体绕轴或铁棒电感具有从绕轴一端经空气到达另一端的磁力线。这些磁力线会在电感磁场范围内的所有导线或PC板铜走线中产生感应电压。铜走线中产生的电压量由以下因素决定:磁场强度、PC铜走线相对于磁场的方向和位置,以及铜走线与电感之间的距离。

FPGA 和稳压器的可靠性取决于散热问题。这些器件的温度主要受待机功耗和总功耗、外部容性负载(仅FPGA)、热阻、环境温度以及气流等因素控制。必须有效管理这些因素,使结温(Tj)始终低于制造商规定的最高温度。

FPGA 电源管理 电压 电流 LDO 电源模块 电路 电容 电感 开关电源 ADI PCB 电阻 PWM 电子 DSP 仿真 变压器 电容器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)